国際特許分類[H01L25/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678)

国際特許分類[H01L25/00]の下位に属する分類

すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439)

装置が27/00〜51/00の2つ以上の異なるメイングループに分類される型からなるもの,例.ハイブリッド回路の形成 (138)

装置がグループ27/00〜51/00の同じメイングループの2つ以上の異なるサブグループに分類される型からなるもの (5,265)

国際特許分類[H01L25/00]に分類される特許

31 - 40 / 836

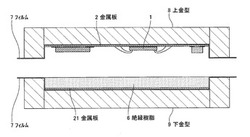

半導体装置の製造方法

【課題】実装効率を維持しながら、信頼性を向上させることを目的とする。

【解決手段】金型内で金属板2に搭載された電子部品の周囲に流動性の高い絶縁樹脂6を圧縮しながら充填し、その後絶縁樹脂6を硬化させることにより、電子部品の損傷や金属線の変形や短絡を防ぎ、配線基板の反りや歪、クラック等の発生を防止して信頼性を向上させながら、高密度に電子部品を配線基板の内部に内蔵することができる。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

半導体装置

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置100を、第1半導体部と、第2半導体部とを備える構成とする。第1半導体部には、接合界面側の表面に形成されかつ第1の方向に延在する第1電極16を設ける。そして、第2半導体部には、接合界面で第1電極16と接合されかつ第1の方向と交差する第2の方向に延在する第2電極26を設ける。

(もっと読む)

半導体装置

【課題】半導体チップをパッケージから切り出すことなく、パッケージ内の半導体チップ毎に、電気的に絶縁された状態で解析を行う

【解決手段】CPUチップ2とメモリチップ3とを電気的に接続する配線11と、CPUチップ2と電源チップ4とを電気的に接続する配線12と、CPUチップ2、メモリチップ3、および電源チップ4を封止する樹脂層21と、樹脂層21の上方に設けられた樹脂層22と、樹脂層22の上方に設けられた樹脂層23とを備え、配線11は、CPUチップ2に接続された一端から、樹脂層23内を通過することなく樹脂層21内と樹脂層22内を通過して、メモリチップ3に接続された他端に到達するように形成され、配線12は、CPUチップ2に接続された一端から、樹脂層21内と樹脂層22内と樹脂層23内を通過して、電源チップ4に接続された他端に到達するように形成される。

(もっと読む)

高周波回路モジュール

【課題】別途シールドケースなどを用いることを必要とせずに、RF回路で発生する高周波ノイズが電源ラインに重畳するなどして、IC素子の誤動作や特性劣化などを引き起こすことを効率よく防止することが可能な高周波回路モジュールを提供する。

【解決手段】アンテナ素子2で送受信される無線通信用の高周波信号を処理するIC素子4、アンテナ素子2とのインピーダンスマッチング用のRF回路3、IC素子4に電源を供給するための電源回路5を含み、RF回路3および電源回路5はいずれも表面実装部品32,561を備えているとともに、RF回路は磁性体基板を素体としてその内部にコイル素子を含むインダクタ基板31を備え、これらがいずれもコア基板6の表面に搭載され、かつ、インダクタ基板31がRF回路3を構成する表面実装部品32と電源回路5を構成する表面実装部品51との間に設けられた構成とする。

(もっと読む)

非接触型ICモジュール

【課題】上下基板の表裏に敷設されたループ状回路の端子部の接続を不要とし、且つ多層であっても薄く平坦な非接触型ICモジュールの提供すること。

【解決手段】少なくとも一方の面にループ状回路を備える第一の基板に、開口部周囲の少なくとも一方の面にループ状回路を備える第二の基板を積層し、前記開口部に露出する第一の基板上にICチップをフェースダウン方式で実装したことを特徴とする非接触型ICモジュールであって、前記開口部に露出する第一の基板上にコンデンサを実装したことを特徴とする非接触型ICモジュールである。

(もっと読む)

半導体装置およびその製造方法

【課題】コストの増大を抑制し、大容量コンデンサを用いる集積回路のモジュールがより小型に形成できるようにする。

【解決手段】半導体基板の上に集積回路が形成された集積回路基板101と、集積回路基板101に積層して接続されたスタック型キャパシタを備えるキャパシタ基板102とを備えるようにしている。キャパシタ基板102は、集積回路基板101の集積回路の形成側に積層してもよく、また、集積回路基板101の集積回路の半導体基板側に積層してもよい。

(もっと読む)

半導体装置および携帯電話機

【課題】送信信号の電力増幅効率を向上させることができる技術を提供する。

【解決手段】半導体チップCHPと配線基板WB2とを積層して、積層された配線基板WB2に出力整合回路を形成する構成と、チップ用幅広貫通電極CWTHE1と基板用幅広貫通電極WTHE1で半導体チップCHPと出力整合回路とを効率良く最短距離で接続するという構成とを取る。これにより、電力増幅モジュールの小型化を図りながら、送信信号の電力増幅効率を向上させることができる。

(もっと読む)

半導体チップ、センサーモジュール及び携帯用電子機器

【課題】主にMEMS技術を利用してダイアフラムを形成したセンサーの機能を有する半導体チップ構造の小型化を行う。

【解決手段】半導体チップは、平面視形状が多角形状をし、外周部のスクライブライン領域の内側に存在する有効領域17の中央にセンサー機能を有し、有効領域17内の2つの頂角の内側に電極パッド21,23が設けられており、ボンディング可能な大きさの正方形状の仮想電極パッドを頂角に最も近づけて形成すると仮想し、頂角の頂点31と、仮想電極パッドにおける頂点31から最も離れた位置との距離をLsとし、頂角の角度を2θとするとき、電極パッド21,23は、半径Rの円形状をし、半径Rは、R<Ls/(1+(1/sinθ))である。

(もっと読む)

パッケージ基板及び半導体パッケージ

【課題】半導体素子に内装されるコンデンサ及びプリント配線基板上に実装される半導体素子の高速動作に過渡電流を供給するために必要なデカップリング用のコンデンサの数を減少するパッケージ基板及び半導体パッケージを提供する。

【解決手段】半導体パッケージ1は、上面に金属層100Vと、金属層100Vの下に設けられた誘電体層101と、誘電体層101の下に設けられる金属層100Gとを有し、金属層100Vの半導体素子搭載領域に半導体素子11を実装し、コンデンサ素子搭載領域に、一端を金属層100Vと接続され、他端をビア102を介して金属層100Gと接続されたコンデンサ12を実装する。

(もっと読む)

31 - 40 / 836

[ Back to top ]