国際特許分類[H01L25/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678)

国際特許分類[H01L25/00]の下位に属する分類

すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439)

装置が27/00〜51/00の2つ以上の異なるメイングループに分類される型からなるもの,例.ハイブリッド回路の形成 (138)

装置がグループ27/00〜51/00の同じメイングループの2つ以上の異なるサブグループに分類される型からなるもの (5,265)

国際特許分類[H01L25/00]に分類される特許

831 - 836 / 836

高周波回路

【目的】 高周波回路モジュールを小型化する。

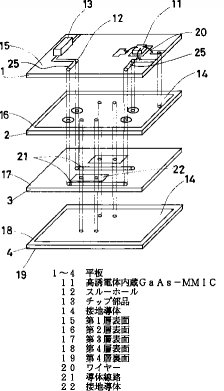

【構成】 多層基板の材料として、アルミナまたはバリウムを含むガラスセラミックを用いる。多層基板の構造は厚さ150μm、縦横7mm角の4層の平板1〜4で構成し、それぞれの層間はスルーホール12で結線している。第1層表面15には高誘電体内蔵GaAs−MMIC11とチップ部品13とマイクロストリップ線路25が設けられている。第2層表面16、第4層表面18にはほぼ全面に接地導体14が配置されている。第3層表面17には、ストリップ線路からなる導体線路21が配置されていて、それぞれの導体線路21間は、接地導体22によって分離されている。第4層裏面19には、印刷抵抗素子によりバイアス抵抗が形成されている。

(もっと読む)

混成半導体集積回路

【構成】高周波集積回路において、半導体集積回路チップ11を出来るかぎり小さくするために、能動素子12,抵抗素子13,容量素子14のみを半導体基板15上に形成し、整合回路に不可欠なスパイラルインダクタンス素子16を形成した高抵抗誘電体基板上に搭載する。

【効果】小型で高性能な、混成型高周波集積回路を実現できる。

(もっと読む)

印刷回路装置

【目的】 低温環境においても、回路基板上の電子部品を急速に加温する。

【構成】 電子部品を接続する配線パターン2を持った回路基板1上に、上記電子部品を予熱するための金属膜のヒータパターン3を設ける。

(もっと読む)

半導体集積回路実装基板

【目的】 高速スイッチング動作時の電源ノイズの発生が抑制され、信頼性が高くかつ半導体集積回路や個別部品の高集積化、高密度実装化を実現した半導体集積回路実装基板を提供する。

【構成】 第1の導電体電極層2と第2の導電体電極層4とこれらの 2つの層間に挟持される誘電体層3とにより形成されるコンデンサが、基板1上に配設されており、基板の最上層の表面に実装された半導体集積回路チップ8とは接続ビア(via)9、10によって接続され、チップコンデンサの表面実装およびその配線のための面積が不要でその分集積回路チップをより多く実装でき、またそれらの配置および結線の自由度も高くでき、半導体集積回路や個別部品の高集積化、高密度実装化が実現できる。

(もっと読む)

半導体装置および放熱フィン

プリント回路基板アセンブリ

本実施例で単層基板(2)からなるDC−DC変換器であるPCBアセンブリ(1)は、高熱発生部品(3)を形成する電力半導体デバイスと、熱放散部品(4)を形成する磁性材料からなる様々なコアを実装している。熱伝導性結合材料(6)の抵抗路が、各熱発生部品(3)の上または下に配設されて、1つの熱放散部品(4)の中に突入しかつその他の側方に延出している。ある実施例では、熱発生部品(3)が熱放散部品(3)の中に収容される。別のPCBアセンブリでは、それ自体が熱発生部品(3)又は熱放散部品(4)のみを担持する追加のプラグインPCBが設けられる。後者の場合、熱発生部品(3)は前記PCBアセンブリ上に追加のプラグインPCBの下側に実装される。 (もっと読む)

831 - 836 / 836

[ Back to top ]