国際特許分類[H01L25/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器を持たない装置 (7,415)

国際特許分類[H01L25/04]の下位に属する分類

装置がグループ27/00に分類された型からなるもの (2,476)

装置がグループ29/00に分類された型からなるもの (4,054)

装置がグループ33/00に分類された型からなるもの

国際特許分類[H01L25/04]に分類される特許

1 - 10 / 885

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体記憶装置

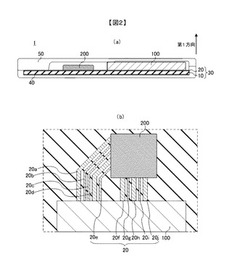

【課題】耐振動性を向上可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置1は、基板30と、基板30上に載置された第1半導体実装部品100と、基板上に載置された第2半導体実装部品200と、第1半導体実装部品100と第2半導体実装部品200に接続されて基板30に設けられた第1配線20a,20d,20f,20h,20jと、第1半導体実装部品100と第2半導体実装部品200に接続されて、第1配線20a,20d,20f,20h,20jの配線幅よりも細い配線幅を有し、基板30に設けられた第2配線20b,20c,20e,20g,20iとを備える。

(もっと読む)

マルチチップモジュール及びその製造方法

【課題】同じはんだ材料を用いながらも基板をヒータで加熱することによるマルチチップ実装を可能にするマルチチップモジュール等を提供する。

【解決手段】マルチチップモジュール10は、一つのPLC20上に複数のLD31,32がそれぞれはんだバンプ41,42を介してかつPLC20の表面200に水平方向に実装されたものである。そして、複数のはんだバンプ41,42の融点Tmが同じであり、PLC20を加熱してからはんだバンプ41,42が融点Tmに達するまでの時間t1,t2はLD31,32ごとに異なる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置を薄型化する技術を提供する。

【解決手段】半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン貫通ビアが形成されたLSIチップが搭載されたパッケージ内において、LSIチップから受動部品までの配線距離を短くする構造およびその製造方法を提供する。

【解決手段】

本発明は、基板上に積層された複数のLSIチップからなる半導体装置であって、シリコン貫通ビアが形成されたLSIチップと、前記シリコン貫通ビアが形成されたLSIチップ上に搭載され、前記シリコン貫通ビアを介して電源経路と電気的に接続する1以上の受動部品と、を有することを特徴とする半導体装置に関する。

(もっと読む)

複合モジュール

【課題】樹脂層により電子部品が封止された複合モジュールが備える実装基板の反りを低減する。

【解決手段】実装基板2の一方主面に実装された電子部品3を封止する樹脂層4を備える複合モジュール1において、樹脂層4の内部にダミー部材5を設けることで、樹脂層4を形成する樹脂の総量を減らし、複合モジュール1が備える実装基板2の反りを低減する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】複数の半導体素子を備えており、半導体素子に流れる電流を検知する際の損失を低減可能な半導体装置及びその製造方法を提供する。

【解決手段】 一実施形態の半導体装置1は、配線パターン22を有する配線基板20と、配線基板上に搭載されるN個(Nは2以上の自然数)の半導体素子10と、配線基板に搭載され、N個の半導体素子のうちから選択されたM個(Mは1以上N以下の自然数)の半導体素子10のうちm個(mは、1以上M未満の自然数)の半導体素子10に流れる電流を検知する電流検知部30A,30Bと、を備える。M個の半導体素子は、配線パターンを介して電気的に並列接続されており、m個の半導体素子は、電流検知部を介してM個の半導体素子のうちの他の前記半導体素子に電気的に並列接続されている。

(もっと読む)

電子部品及びその製造方法

【課題】 ロジックチップとメモリチップとを実装しながら、メモリチップで誤動作を生じさせない電子部品及びその製造方法を提供することにある

【解決手段】 放熱部材300がロジックチップ90A及びメモリチップ90B上に取り付けられる。放熱部材300には、メモリチップ90Bの上面と当接する部位に開口308が設けられている。このため、ロジックチップ90Aからの熱が放熱部材300を介してメモリチップ90Bへ伝わり難いため、ロジックチップからの熱的影響でメモリチップが誤動作し難くなる。

(もっと読む)

半導体装置の製造方法、半導体装置及び半導体装置の製造用治具

【課題】長尺接続子により直線上に配列された複数の半導体チップを半田付けにより共通接続する場合において、長尺接続子の撓みを防止して当該長尺接続子と各半導体チップとの間隔を適正な間隔に保持する。

【解決手段】長尺接続子110の接続板部113を当該長尺接続子110の先端部の側に位置する半導体チップ133よりもさらに先方にまで延長することによって形成された延長部150の下面側に突起部114を有する長尺接続子110と、リードフレーム120を載置するリードフレーム載置面200aに長尺接続子110の突起部114を当接させるための突起当接部210を有する台座200とを用いて、長尺接続子110の突起部114を台座200の突起当接部210に当接させるようにリードフレーム120を台座200に載置した状態で半導体チップ131〜133の各上面と長尺接続子110の接続板部113の下面とを半田付けする。

(もっと読む)

リードフレームおよび半導体装置

【課題】チップをGND接続して電気的特性を安定化すると共に、パッケージを小型化するためのリードフレームおよび半導体装置を提供する。

【解決手段】表面に設けられたチップ搭載領域11と、前記チップ搭載領域と同一面内方向の複数の凹凸部を含むリード領域13Aと、前記凹部に配置された端子12とを備え、前記リード領域の表面からの厚みは、前記端子の表面からの厚みよりも小さいリードフレーム10。

(もっと読む)

1 - 10 / 885

[ Back to top ]