国際特許分類[H01L27/04]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153)

国際特許分類[H01L27/04]の下位に属する分類

複数の個々の構成部品を反復しない形で含むもの (2,326)

1種類の半導体構成部品だけを含むもの (8,288)

複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/04]に分類される特許

1,001 - 1,010 / 9,686

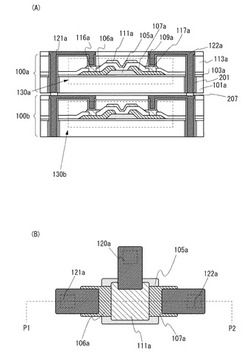

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置

【課題】半導体装置の耐圧を向上させる。

【解決手段】半導体装置は、ドレイン層の表面から内部にかけて、ドレイン層に選択的に設けられたドリフト領域と、ドリフト領域の表面から内部にかけて、ドリフト領域に選択的に設けられたベース領域と、ベース領域の表面から内部にかけて、ベース領域に選択的に設けられた、ソース領域と、ドレイン層の主面に対して略平行な方向に、ソース領域の一部から、ソース領域の一部に隣接するベース領域を貫通して、ドリフト領域の一部にまで到達するトレンチ状のゲート電極と、ベース領域の不純物濃度よりも高い濃度の不純物が含まれ、ドリフト領域の表面に選択的に設けられたコンタクト領域と、ドレイン層に接続されたドレイン電極と、ソース領域およびコンタクト領域に接続されたソース電極と、を備え、コンタクト領域は、ドレイン層側からドリフト領域に向かって延在し、ドレイン層と接触していない。

(もっと読む)

半導体装置

【課題】検出精度が低下することを抑制することができる半導体装置を提供する。

【解決手段】メインセル部10aとセンスセル部10bとのセル数の比をセル比とし、ドリフト層3の抵抗率をρとし、電流検出抵抗9の両端電圧の経時変化率をxとしたとき、{センスセル部(10b)/メインセル部(10a)}のセル比が、{(x+0.22ρ+10.08)/224.38}2で導き出される値とされ、ドリフト層3の抵抗率ρが30Ω・cm以上であって、かつ電流検出抵抗9の両端電圧の経時変化率xが+5〜−5%である半導体装置とする。

(もっと読む)

半導体集積回路装置

【課題】製造ばらつきによる出力電圧の精度劣化の補正のため、従来技術ではテストコストの増大や回路規模の増大化を招く問題が発生していた。

【解決手段】n(2以上の正の整数)桁のデジタル信号を電圧信号に変換するDAコンバータを有する半導体集積回路装置であって、それぞれが前記デジタル信号の各ビット桁に対応し、前記デジタル信号に応じて前記電圧信号を生成するn個の電圧生成素子を有し、前記n個の電圧生成素子のうちビット桁が最下位からk(k≦n)番目に対応する電圧生成素子の生成する電圧は、ビット桁が最下位からk−1番目に対応するk−1個の電圧生成素子の生成する電圧に第1の所定の値を足した電圧よりも低くなることを特徴とする半導体集積回路装置。

(もっと読む)

半導体装置の製造方法

【課題】前工程においてトランジスタごとに不純物の種類や量を変えることによる、製造コストや製造時間の増大を抑制する。

【解決手段】本発明による半導体装置の製造方法は、第1の閾値電圧及び第1のドレイン・ソース間電流を呈するようなデバイスパラメータをもって設計された第1のトランジスタを含む半導体回路を形成する半導体回路形成工程(ステップS11)と、第1のトランジスタにストレス電圧を印加して第1の閾値電圧とは異なる第2の閾値電圧及び前記第1のドレイン・ソース間電流とは異なる第2のドレイン・ソース間電流の少なくとも一方を第1のトランジスタが呈するようにする特性制御工程(ステップS14)と、第1のトランジスタが第2の閾値電圧及び第2のドレイン・ソース間電流の少なくとも一方を呈する状態で出荷する出荷工程(ステップS16)とを備える。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

保護装置

【課題】 USBコネクタと被保護部品間の信号ラインに接続されるESD破壊の保護装置として、双方向pn接合ダイオードが用いられるが、従来の構造では製造工程が複雑、煩雑で保護装置の低コスト化や耐圧の汎用性に限界があった。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面に互いに離間する第1n+型不純物領域および第2n+型不純物領域を設け、これらの直下にこれらの底面より小さい第1p++型不純物領域と第2p++型不純物領域を設け、第1n+型不純物領域とコンタクトし、入力端子に電気的に接続する第1電極と、第2n+型不純物領域にコンタクトし、接地端子に電気的に接続する第2電極とを設ける。第1n+型不純物領域および第2n+型不純物領域は140μm以上離間され、それぞれ角丸四角形状でp+型半導体基板の対角線に沿って配置される。

(もっと読む)

抵抗値補償方法、抵抗値補償機能を有する回路、回路の抵抗値試験方法、抵抗値補償プログラム、回路の抵抗値試験プログラム及びシステム

【課題】簡易で精度の高いODT回路の抵抗補償方式を提供することを目的とする。

【解決手段】複数のトランジスタの組み合わせによって所望の抵抗値と同等の抵抗値を実現するODT回路200であって、組み合わせるべきトランジスタを順次選択することにより、選択されたトランジスタによって実現される抵抗値を順次変化させる構成である。

(もっと読む)

モータ制御用半導体装置

【課題】モータ制御用半導体装置に対するコンタクト用ピンからの影響を低減する

【解決手段】ホール素子102からの出力のオフセット電圧を取り除くオフセットキャンセル回路104に含まれるオシレータ回路12と、オフセットキャンセル回路104からの出力信号を受けて、当該出力信号と基準信号とを比較して比較信号を生成して出力するコンパレータ回路106と、モータを駆動するための駆動信号を生成して出力する出力回路110と、モータの制御に関係しないテスト回路112と、を有し、オシレータ回路12の回路パターン上、コンパレータ回路106の回路パターン上、及び、テスト回路112の回路パターン上のいずれか1つに重なるようにパルス幅変調信号の入出力パッドP1を形成する。

(もっと読む)

半導体装置及びこれを用いた電気回路、電気回路の制御方法

【課題】消費電力を増大させずにオンチップでHEMTの動作状況をモニターする。

【解決手段】

この半導体装置10においては、第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層側に、2次元電子ガス(2DEG)層13が形成される。この半導体装置10において、電子は、電子供給層12の表面に形成された第1の主電極であるソース電極14と、同様にこの表面に形成された第2の主電極であるドレイン電極15との間を、この2DEG層13を通って流れる。ゲート電極16とソース電極14との間の電子供給層12上に電位検出電極17が設置される。この電位検出電極17には、動作時にこの電位検出電極17に流れる電流がドレイン電流と比べて無視できる程度となるような、充分に高い抵抗値をもつ抵抗18が接続される。

(もっと読む)

1,001 - 1,010 / 9,686

[ Back to top ]