国際特許分類[H01L27/088]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 1種類の半導体構成部品だけを含むもの (8,288) | 電界効果構成部品のみを含むもの (6,291) | 構成部品が絶縁ゲートを有する電界効果トランジスタであるもの (5,861)

国際特許分類[H01L27/088]の下位に属する分類

相補型MIS電界効果トランジスタ (2,948)

国際特許分類[H01L27/088]に分類される特許

1 - 10 / 2,913

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

炭化珪素半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法及び半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

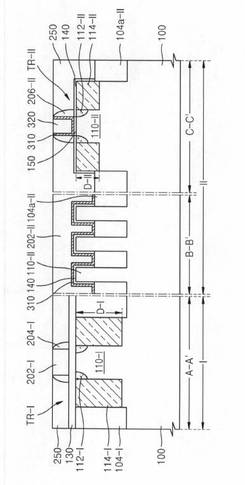

【解決手段】高電圧領域及び低電圧領域を有する半導体基板100と、高電圧領域に形成され、第1活性領域110-I、第1ソース/ドレイン領域114-I、第1ゲート絶縁膜130及び第1ゲート電極202-Iを有する高電圧トランジスタTR-Iと、低電圧領域に形成され、第2活性領域110-II、第2ソース/ドレイン領域114-II、第2ゲート絶縁膜310及び第2ゲート電極320を有する低電圧トランジスタTR-IIとを備え、第2ソース/ドレイン領域は、第1ソース/ドレイン領域より薄い厚さを有することを特徴とする半導体素子。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基準電圧発生回路を構成するエンハンスメント型MOSFETとデプレッション型MOSFETとの間の温度特性の差を小さくすることができ、基準電圧発生回路の出力電圧の温度特性を改善することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板6上においてRef回路領域8およびCMOS領域7に跨るようにゲート絶縁膜66を形成した後、CMOS領域7の部分を選択的に除去する。次に、熱酸化により、ゲート絶縁膜66が除去されたCMOS領域7に第1ゲート絶縁膜12を形成し、同時に、Ref回路領域8に残っているゲート絶縁膜66を厚くして第1ゲート絶縁膜12よりも厚い第2ゲート絶縁膜13を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

1 - 10 / 2,913

[ Back to top ]