国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

1,001 - 1,010 / 3,785

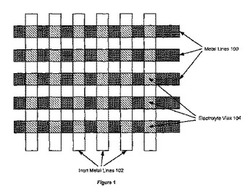

三次元メモリアレイ積層構造体

【課題】 改善された三次元メモリ(例えば、RRAM)アーキテクチャを提供すること。

【解決手段】 メモリデバイスが、平面基板と、平面基板の上方の複数の水平な導電性平面と、複数の水平な導電性平面と交互に配置される複数の水平な絶縁層とを備える。複数の導電性平面および絶縁層と直角である垂直な導電性列のアレイが、複数の導電性平面および絶縁層における開口部を通過する。メモリデバイスは、複数のプログラム可能なメモリ素子を備え、それぞれのメモリ素子が、水平な導電性平面の1つをそれぞれの垂直な導電性列に連結する。

(もっと読む)

半導体装置の製造方法

【課題】 STIを利用して形成した素子分離膜がウエットエッチング工程により目減りすることを出来るだけ抑制しながら半導体装置を製造する。

【解決手段】 犠牲酸化膜の形成とウエットエッチングによる剥離、及び/又は、二酸化珪素膜の形成とウエットエッチングによる剥離を行う半導体装置の製造プロセスにおいて、犠牲酸化膜及び/又は二酸化珪素膜の形成を、プラズマ処理装置の処理容器内で、酸素を含む処理ガスを用いて生成させたO(1D2)ラジカルが支配的なプラズマにより行う。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

金属ナノ粒子を有する抵抗変化メモリ

【課題】抵抗変化メモリ素子の抵抗値のばらつきがなく、動作電圧の制御が可能な抵抗変化メモリ素子を提供する。

【解決手段】第1電極100と、第1電極100上に形成された遷移金属酸化物の抵抗変化層110と、抵抗変化層110上に形成された第2電極130、及び抵抗変化層110内に形成される金属ナノ粒子120を含む抵抗変化メモリ素子であって、フィラメント電流経路140は第2電極130と金属ナノ粒子120間でのみ形成される。これにより、メモリ素子の抵抗値を安定化することができる。

(もっと読む)

半導体装置の駆動方法

【課題】電荷蓄積層での電子の蓄積または放出が十分でない場合に、不揮発性メモリ素子に保持された記憶状態の正誤を判定し、誤ったデータを読み出すことによる不良を低減する。

【解決手段】メモリセル領域104と、テスト領域105と、を含む半導体記憶回路103と、制御回路と、を有し、制御回路は、メモリセルへのデータの書き込み、第1の領域105Aへの第1の記憶状態の書き込み、または第2の領域105Bへの第2の記憶状態の書き込みを行うための第1の動作を行い、第1の領域及び第2の領域からの第1の記憶状態または第2の記憶状態の読み出しを行うための第2の動作を行い、メモリセルからのデータの読み出しを行うための第3の動作を行い、第2の動作において、第1の領域からの読み出しが第1の記憶状態であるか、または第2の領域からの読み出しが第2の記憶状態であるかに応じて、第3の動作の正誤を判定する。

(もっと読む)

半導体装置

【課題】半導体装置の歩留まりを向上させること若しくは製造コストを低減すること又は集積回路の面積を低減する半導体装置を提供する。

【解決手段】半導体装置が有するメモリ素子10のメモリ層12及び抵抗素子20の抵抗層22が同一材料によって構成される。そのため、メモリ層12と、抵抗層22とを同一工程によって形成することで、半導体装置の作製工程数を低減することができる。結果として、半導体装置の歩留まりを向上させること又は製造コストを低減することができる。また、半導体装置は、抵抗値の高い抵抗成分を備えた抵抗素子20を有する。そのため、半導体装置が有する集積回路の面積を低減することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

半導体装置およびその製造方法

【課題】PMOS領域における素子分離膜のライナー窒化膜の除去を行う従来技術による問題を解決した半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板20をエッチングして複数のトレンチを形成するステップと、複数のトレンチ内に第1絶縁膜24Aを埋め込んで第1素子分離膜を形成するステップと、一部のトレンチ(CELL又はPERI NMOS領域のトレンチ)内に埋め込まれた第1絶縁膜24Aをリセスするステップと、リセスされたトレンチの全面にライナー膜26A、27Aを形成するステップと、ライナー膜26A、27Aが形成されたトレンチ内に第2絶縁膜28を埋め込んで第2素子分離膜を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】高速動作のために低電圧で相対的に大きな電流駆動力を必要とするMISFETと高耐圧を必要とするMISFETを有する半導体装置において、各素子を、それぞれの素子特性の向上を図りつつ簡素化した工程で製造する。

【解決手段】低耐圧MISFETのゲート電極4およびMONOSメモリのメモリゲート電極8のそれぞれの側壁にサイドウォールA、Bを形成する際、専用のマスクを用いず、低温下で堆積することのできる酸化膜をフォトレジスト膜が形成されたシリコン基板1上に形成し、ゲート電極4およびメモリゲート電極8のそれぞれの側壁に幅の違うサイドウォールA、Bを形成する。

(もっと読む)

半導体装置

【課題】相変化素子に対する動作マージンを向上させる。

【解決手段】例えば、相変化素子を結晶状態にするセット動作(SET)の際に、相変化素子に対して、始めに素子を溶融するために必要な電圧Vresetのパルスを印加後、続けて、Vresetよりも低く素子を結晶化するために必要な電圧Vsetのパルスを印加する。そして、この電圧Vsetの大きさを外気の温度に依存して変化させ、高温(TH)になる程電圧Vsetの大きさが小さくなるようにする。これによって、セット動作と、素子をアモルファス状態にするリセット動作(RESET)との間の書き込み動作マージンが向上する。

(もっと読む)

1,001 - 1,010 / 3,785

[ Back to top ]