国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,781 - 3,785 / 3,785

強誘電体メモリ

【目的】この発明は、酸化物強誘電体表面の還元反応、変質を阻止するとともに、MOSシンター工程において強誘電体薄膜と上下電極間の剥離を防止することを主要な目的とする。

【構成】半導体基板(1) と、この基板(1) 上に設けられ、下部電極(10),酸化物強誘電体薄膜(11),上部電極(12)の順次積層して構成される誘電体薄膜キャパシタ(9) と、このキャパシタ(9) 表面に被覆された、アルミニウム,シリコンもしくはチタンの窒化物薄膜を主要な構成要素とする保護膜(12)とを具備したことを特徴とする強誘電体メモリ。

(もっと読む)

単一電子帯電効果を利用した記憶回路とその製造方 法

【目的】 電子を単一電子帯電効果によって独立した電極に蓄えることを利用するものである。従来素子に比べ、集積度・動作速度の向上を可能ならしめる記憶回路を構成する。

【構成】 情報は、グランド線12に接続された2つの直列接続のトンネル接合21、22、書き込み線13に接続されたコンデンサー31、そして、読み出し回路03に接続されたコンデンサー32が、それぞれ並列に接続された電気的に独立した電極01に、電子を蓄えることによって保持される。直列に接続されたトンネル接合により、書き込み電圧Vw に対し、電子数がNまた(N+1)個が安定に蓄えられる双安定領域が存在することを用いて、書き込み電圧のわずかな変化に対して記憶が失われないような記憶回路を構成する。電子が安定に独立した電極に保たれている。読み出しには単一電子トンネルトランジスターを用いる。

(もっと読む)

メモリ装置

【目的】 類似した機能のメモリ装置に容易に差し替え可能とする。

【構成】 構成内容は異なるが、実装用の端子に対しピンコンパチブルとして互換性を保持する。基板1に代替え用の表面実装形のフラッシュEEPROM素子2a及び2bを実装し、対向するピンは相互の接続が最短距離となるように配置し、基板1に設けたピン3がピンコンパチブルとなるようにする。また、必要に応じてそのピン3をソケット5に挿入し、ソケット付きの状態で使用する。

(もっと読む)

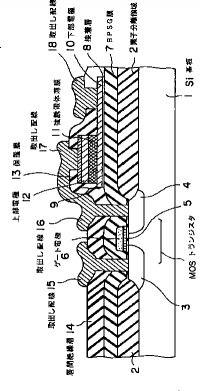

半導体装置

【目的】内部回路から発生する電源ノイズを低減するためのバイパスコンデンサを、半導体チップ内部に形成してシステムの小型化およびノイズ低減能力の向上を図る。

【構成】多層配線構造の半導体チップの外周に沿って、層間絶縁膜4の一部に薄い層間絶縁膜4aを設けて、対向する下層配線3と上層配線6とをそれぞれ電源配線と接地電位配線として、バイパスキャパシタとする。

【効果】半導体チップの面積を増加することなく、電源ノイズを低減するための大きな容量値をもつバイパスキャパシタを形成することができる。従来半導体チップの外部に実装していたキャパシタを削減して、システムを小型化することができる。半導体チップ内部にバイパスコンデンサを形成することにより、電源ノイズ低減効果が向上するとともに、EMI(電波雑音干渉)発生の低減を図ることができる。

(もっと読む)

集積回路装置及びその製造方法

【目的】 集積回路装置及びその製造方法に関し、絶縁膜をレジスト・プロセスから保護する為の保護膜を薄くしても、充分な保護が可能であるようにして耐圧低下を防止しようとする。

【構成】 シリコン半導体基板1の上に順に積層して形成されたゲート絶縁膜3及び該ゲート絶縁膜3を保護する為のアモルファス・シリコン(α−Si)からなる保護膜8と、該アモルファス・シリコンからなる保護膜8並びに該ゲート絶縁膜3を貫通して該シリコン半導体基板1に達するコンタクト窓3Aとを備えている。

(もっと読む)

3,781 - 3,785 / 3,785

[ Back to top ]