国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

1 - 10 / 3,785

半導体装置の製造方法及び半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法及び半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体集積回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

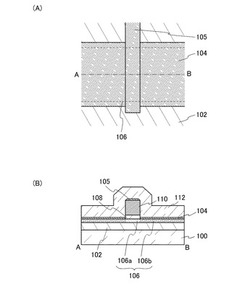

FinFETを形成する方法およびFinFET構造

【課題】 ゲートの平面性が改善されたFinFETおよび形成方法を提供する。

【解決手段】 不要なフィンを除去する前にフィンのパターン上にゲートが配置される。リソグラフィ技法またはエッチング技法あるいはその両方の組み合わせを使用して、不要なフィンを除去することができる。残りのフィンの全部または一部を併合することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

1 - 10 / 3,785

[ Back to top ]