国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

31 - 40 / 855

半導体装置

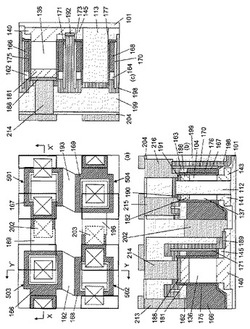

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

メモリ装置

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

半導体集積回路装置

【課題】低電源電圧でもSNMと書き込みマージンを両立させたSRAMを備える。

【解決手段】SRAMは、複数列に対応して設けられた複数のセル電源線、電源電圧を供給する電源線、及び前記複数のセル電源線にそれぞれ対応して設けられ、各々はその対応するメモリセル電源線と前記電源線との間を電気的に接続する複数の電源回路を含む。メモリセルの各々は、第1及び第2のPチャネル型トランジスタと、第1ないし第4のNチャネル型トランジスタと第1及び第2の記憶ノードとを有するCMOSラッチ回路で構成される。電源回路は、第1の状態時にはその接続するセル電源線に第1の電圧を供給し、第2の状態時にはその接続するセル電源線に前記第1の電圧よりも低い第2の電圧を供給する、

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

情報処理装置及び半導体記憶装置

【課題】製造コストの低減に対して有利な情報処理装置及び半導体記憶装置を提供する。

【解決手段】実施形態によれば、ホスト装置と、前記ホスト装置にバスを介して接続された半導体記憶装置とを備える情報処理装置であって、前記ホスト装置は、メインメモリを備え、前記半導体記憶装置は、第1の論物変換テーブル及びデータを格納する不揮発性半導体メモリと、前記第1の論物変換テーブルの一部である第2の論物変換テーブルを格納する記憶部と、前記第2の論物変換テーブルを参照し前記不揮発性半導体メモリにアクセスする制御部とを備え、前記第1の論物変換テーブルの少なくとも一部が前記メインメモリ上にコピーされ、前記第2の論物変換テーブルに前記制御部がアクセスする論理アドレス又は物理アドレスが登録されていない場合、前記メインメモリ上の第3の論物変換テーブルの一部が前記第2の論物変換テーブルにコピーされる。

(もっと読む)

半導体記憶装置

【課題】TFTなどのトランジスタ特性がばらつく状況や、RF回路から電源が供給され

電源が安定しない状況で、SRAMを作製する場合、従来の1つのメモリセルに6つのト

ランジスタの構成では読み出し時にメモリセルが保持する値が書き換わる誤書き込みが発

生してしまう。

【解決手段】SRAMのメモリセルは、書き込みの回路と読み出しの回路を分離する事に

より、SRAMの誤書き込みを防ぎ、安定した動作を行うことを可能にする。また、書き

込みのタイミングを考慮する事により、誤書き込みを起こさず、より確実に書き込みの動

作を行うことが可能なSRAMを提供する。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

31 - 40 / 855

[ Back to top ]