国際特許分類[H01L27/11]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | 電界効果構成部品を含むもの (11,969) | スタティックランダムアクセスメモリ構造 (855)

国際特許分類[H01L27/11]に分類される特許

851 - 855 / 855

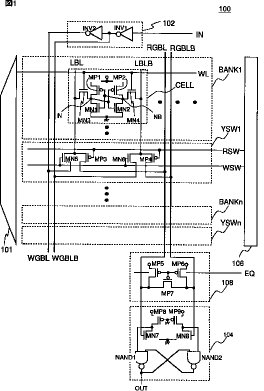

半導体記憶装置、半導体装置、データ処理装置及びコンピュータシステム

半導体記憶装置、半導体装置、データ処理装置及びコンピュータシステム

【課題】 メモリセル又はメモリセルアレイの面積の増大を抑さえて、キャッシュメモリの高速なストア処理を実現することである。

【解決手段】 メモリアレイ(BANK1)と、センスアンプ(104)に接続される第1のグローバルビット線(RGBL)と、ライトアンプ(102)に接続される第2のグローバルビット線(WGBL)と、前記複数のビット線(LBL)を前記第1のグローバルビット線(RGBL)及び第2のグローバルビット線(WGBL)に選択的に接続する選択回路(YSW1)とを具備する。

【効果】 読み出しと書き込みのためのビット線の充放電を並列に行うことができるため、読み出しと書き込みの連続動作を高速化でき、1サイクルで終えることが可能となり、1サイクルストアが実現できる。

(もっと読む)

完全CMOS型SRAM装置

【目的】 セル面積の縮小、すなわち高集積化を図り、しかも信号処理の高スピード化を図ることができる完全CMOS型SRAM装置を提供すること。

【構成】 SRAMセルの構成要素であるP型トランジスタのP型不純物拡散層4aとN型トランジスタのN型不純物拡散層4bとが、同一パターンの半導体薄膜層16内に直接PN接合(ダイオード接続)するように形成してある。PN接合する部分の近くのN型不純物拡散層4bまたはP型不純物拡散層4aまたはこれらの双方に対して、半導体薄膜層の上部に形成されるゲート電極6a,6a’の一部が、コンタクトホール8a,8bを通して接続してある。

(もっと読む)

半導体装置

半導体記憶装置およびその製造方法

851 - 855 / 855

[ Back to top ]