国際特許分類[H01L27/118]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853) | マスタースライス集積回路 (89)

国際特許分類[H01L27/118]に分類される特許

1 - 10 / 89

半導体集積回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

メモリセル

【課題】拡散層等のバルクが固定であってメタル層、コンタクト層の少なくとも何れか1層を変更して複数の仕様に対応可能なメモリセルを提供すること。

【解決手段】メモリユニットが列方向に沿って鏡面対称に行方向に沿って並置されて、2行2列に配置されメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第4拡散層を備え一対の記憶ノードが構成される。第1および第2ワード線は第1〜第4拡散層の両端部外方に配置される。第1及び第2ワード線の間に行方向に沿って第1のメタル配線領域が確保され、第1メタル層が配線可能とされる。列方向に隣接配置されるメモリユニットの境界領域でありは第3、第4拡散層が配置される列方向の位置には列方向に沿って第2のメタル配線領域が確保され、第2メタル層が配線可能とされる。

(もっと読む)

半導体集積回路装置

【課題】内部コアエリアのトランジスタを犠牲にすることなく、周辺エリアのトランジスタを用いてリップルフィルタによる電源供給回路を構成する。

【解決手段】入出力回路を構成するためのトランジスタが配列されてなる周辺エリア(図2の12に相当)をチップ上に有する半導体集積回路装置であって、ドレインを電源に接続し、ソースを負荷側に接続し、ゲートを容量素子(図2のC1)を介して交流的に接地する第1のトランジスタ(図2のMN1)と、容量素子をゲート・基板間によって形成する第2のトランジスタと、を周辺エリアに備える。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

集積回路の設計および製造のための方法およびアーキテクチャ

【課題】集積回路の設計及び製造の問題点に対応する新規の設計プラットフォームを提供する。

【解決手段】集積回路の設計のためのシステム。構造マルチプロジェクトウエハ5(SMPW)は、あらかじめ製造されており且つあらかじめ確認されている多数の機能ブロックを有する。SMPWは、ユーザーが、該ユーザーの要求に応じて、SMPWの異なるブロックをカスタマイズ及びプログラムできるように、コンタクト層まで形成される。SMPWのプロバイダーは、SMPWの在庫を保持する。もし、SMPWの一つがユーザーのIC設計要求の全てを満足できるか、又は市場/コンセプトの確認やIPの確認のような、ユーザーのIC設計プロセスの中間ステップに役立つならば、SMPWは、上記ユーザーへ提供される。ユーザーは、1-3ヶ月のサイクルタイムを有する合理的な設計フローを用いて直接生産へ進む。又は、ユーザーは、もっと長いサイクルタイムを有する普通の設計フローを用いる生産へ進む。

(もっと読む)

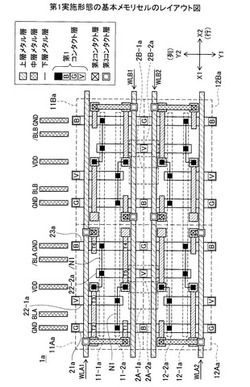

マスタスライス方式メモリセル

【課題】複数種類の回路構成をマスタスライス方式で対応可能なメモリセル専用のマスタスライス方式メモリセルを提供すること。

【解決手段】メモリユニットが2行2列に配置されてメモリセルを構成する。メモリユニットは、行方向に沿って並置され列方向に伸長される第1〜第3拡散層を備え、各拡散層で並列接続のトランジスタが構成される。第1および第2ワード線は第1〜第3拡散層の両端部外方に配置される。第1〜第3拡散層の第1コンタクト層とゲート層の第2コンタクト層との間、第1コンタクト層と第1/第2ワード線との間に、行方向に沿って第1のメタル配線領域が確保される。第1のメタル配線領域には、第2または第3メタル層の何れかが配線可能である。第1及び第2拡散層、第2及び第3拡散層の間には、列方向に沿って第2のメタル配線領域が確保される。第2のメタル配線領域には第3メタル層が配線可能である。

(もっと読む)

半導体装置およびその製造方法

【課題】中間配線層までの配線が行われているマスターウェーハを使用しても、最終製品の歩留りを高い精度で予測することができる半導体装置およびその製造方法を提供する。

【解決手段】多層配線構造の中間配線層までを使用して機能動作を行うように設計された機能ブロック(SRAMマクロ11、ロジックブロック12、ロジックブロック13、IPブロック14)を搭載したマスターウェーハを使用するマスタースライス方式の半導体装置は、この中間配線層に試験用パッドTPを備え、この試験用パッドTPが、各機能ブロックに接続される。

(もっと読む)

半導体装置

【課題】マスタースライス配線用の配線トラックの領域をより有効に活用することを可能にした半導体装置を提供する。

【解決手段】第1の方向に並んで配置された複数の論理回路の入力端子のそれぞれが第1の方向に直交する第2の方向について同じ位置に配置され、活性化される論理回路の入力端子のそれぞれが第1の方向に延在する入力配線に接続され、非活性化される論理回路の入力端子が非活性配線と接続されており、入力配線と非活性配線とは第2の方向について互いに実質的に等しい位置に配置されている構成である。

(もっと読む)

埋め込みデジタルストリップチップ

集積回路(IC)を提供する。ICは、プログラマブル論理セルのアレイを有する、第1の領域を含む。ICはまた、ICの中に組み込まれ、かつ第1の領域と通信している、第2の領域も含む。第2の領域は、標準論理セルと、ベースセルとを含む。一実施形態において、標準論理セルは、既知のプロトコルに適応するように組み立てられる、または相互接続される。ベースセルは、ベースセルによってサポートされる新生の通信プロトコルの修正に適合するように、構成可能な論理を含む。第2の領域は、一実施形態では、第1の領域に埋め込むことができる。別の実施形態において、第2の領域は、第1の領域の周囲に画定される。構成可能な論理は、新生の通信プロトコルが進化して修正されるにつれて、プロトコルの変更に適応させるようにICを修正することができるように、金属マスクプログラム可能な相互接続を有する、ハイブリッド論理素子で構成されてもよい。  (もっと読む)

(もっと読む)

半導体装置

【課題】異なるドメインのそれぞれに、独立して電源電圧を供給することが可能で、クロックジッタを抑制して、ロジックの動作速度の低下を防止した半導体装置を提供する。

【解決手段】電源バンプBP1およびBP2に電気的に接続される電源線WL1を、電源バンプBP1およびBP2の横方向の配列に平行して複数配設し、電源線WL1に電気的に接続される下層の電源線WL2を、電源線WL1に平面視的に直交するように互いに平行して複数配設する。そして、電源バンプBP1の配列を挟む最近傍の2つの電源線WL1に電源電圧V1およびV2を割り付け、電源バンプBP2の配列を挟む最近傍の2つの電源線WL1に電源電圧G1およびG2を割り付ける。電源線WL2は、電源線WL1に平面視的に直交するように互いに平行して配設する。

(もっと読む)

1 - 10 / 89

[ Back to top ]