国際特許分類[H01L27/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体以外のもの,例.絶縁体本体 (2,168)

国際特許分類[H01L27/12]の下位に属する分類

薄膜または厚膜受動構成部品と組合せたもの

国際特許分類[H01L27/12]に分類される特許

1 - 10 / 2,168

SOI基板の作製方法および貼り合わせ装置

【課題】半導体基板と、半導体基板とは異なる熱膨張係数を有する基板を用いてSOI基板を作製するにあたり、両基板を貼り合わせた後の加熱処理において、両基板の熱膨張係数の差異に起因して基板に破壊が生じたり、貼り合わせた両基板が剥がれてしまうことを抑制する。

【解決手段】半導体基板と、半導体基板とは異なる熱膨張係数を有する基板のうち、熱膨張係数の小さい基板の温度よりも熱膨張係数の大きい基板の温度を高くした状態で、両基板を貼り合わせる。また、両基板の温度を室温より高く、かつ、両基板を貼り合わせた後の加熱処理の温度よりも低くした状態で貼り合わせる。これにより、両基板を貼り合わせた後の加熱処理において両基板の膨張量の差を少なくすることができるため、基板の破壊や剥がれを抑制することができる。

(もっと読む)

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

SOIウエハおよびSOIウエハの製造方法

【課題】除電構造と素子分離構造とを有するSOIウエハを、従来より少ない工程で製造することができるSOIウエハの製造方法の提供。

【解決手段】SOIウエハの周縁部分に活性層用半導体層および絶縁酸化膜を貫通する除電用トレンチをエッチングで形成すると同時に、当該周縁部分より内側の内側部分に上記活性層用半導体層を貫通し上記絶縁酸化膜に到達する素子分離用トレンチをエッチングで形成するトレンチ形成ステップを備え、上記トレンチ形成ステップは、上記周縁部分におけるエッチングレートが、上記内側部分におけるエッチングレートよりも高いことを特徴とする。

(もっと読む)

素子形成用基板及びその製造方法

【課題】貼り合わせ界面における界面準位密度を低減することができ、LSIの更なる低消費電力化及び高速化等に寄与する。

【解決手段】絶縁膜上にGe層やSiGe層を形成した素子形成用基板の製造方法であって、Ge基板11の表面上にSi膜12を形成する工程と、Si膜12上に高誘電率絶縁膜13を形成する工程と、Si膜12及び高誘電率絶縁膜13が形成されたGe基板11と表面に酸化膜22が形成された支持基板21とを、高誘電率絶縁膜13と酸化膜22とを接触させて接着する工程と、支持基板21に接着された前記Ge基板11を、該Ge基板11の裏面側から研磨して薄くする工程とを含む。

(もっと読む)

化合物半導体

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。Si基板上のシリコン酸化膜の上に単結晶のSiC膜を形成し、トレンチによる絶縁物分離構造とし、その中に結晶欠陥が多くてもその影響を避ける新構造の素子の発明である。

【解決手段】SiC膜に形成したMOSFETなどの半導体素子を構成しているPN接合面において基板面と並行となる面にあるPN接合に印加される電界が、SiC膜が形成されているシリコン酸化膜や基板となるSi層により緩和されて、さらには基板電位をドレイン電圧とは逆方向の電位とすることにより大きく電界緩和されて、SiC膜に発生している基板と垂直方向の結晶欠陥の結晶欠陥降伏電圧以下とすることを特徴とする素子構造を持った半導体装置。

(もっと読む)

半導体ウェハ

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

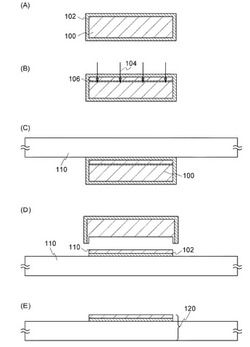

SOI基板の作製方法および作製装置

【課題】単結晶半導体基板とベース基板の界面に空気層が残ることに起因した、ベース基板から単結晶半導体基板を引き剥がした際に生じる転載不良領域の発生が抑制された、高品位なSOI基板の作製方法および作製に用いる貼り合わせ装置を提供することを課題とする。

【解決手段】ボンド基板を、ベース基板の設置面に対して傾斜角を持たせた状態で貼り合わせる。これにより、貼り合わせ開始箇所を限定できる。また、ボンド基板の一部が支持台からはみ出し、且つ、支持台からはみ出した部分がベース基板に最も近くなる状態にボンド基板を設置した。これにより、ボンド基板とベース基板の接触箇所下部には支持台がなく、ボンド基板の一部は支持台の端部を支点として支持台から浮かんだ状態となり、ベース基板に近づいた部分から順次貼り合わせが進むため、ボンド基板とベース基板の界面に空気層残りが生じることなく安定した貼り合わせを行うことができる。

(もっと読む)

SOIウェーハ

【課題】SOIウェハとウェーハ製造設備で使用される搬送ステージと間における静電吸着現象の発生を防止することができるSOIウェーハを提供する。

【解決手段】SOIウェーハ1は、表面全体にシリコン酸化膜11が成膜された単結晶シリコンからなる支持基板用半導体ウェーハ10、支持基板用半導体ウェーハ10の第1主面に形成された単結晶シリコンからなる活性層22、及び支持基板用半導体ウェーハ10の活性層22が形成された第1主面と対向する第2主面に形成された導電性を有する導電性膜33を備える。

(もっと読む)

SOIウェーハおよびSOIウェーハの製造方法

【課題】SOIウェーハとウェーハ製造設備で使用される搬送ステージと間における静電吸着現象の発生を防止することができるSOIウェーハおよびそのSOIウェーハの製造方法を提供する。

【解決手段】SOIウェーハ1は、単結晶シリコンからなる支持基板半導体11と表面に成膜されたシリコン酸化膜12bとを含む支持基板用半導体ウェーハ10、支持基板用半導体ウェーハ10の第1主面に形成された単結晶シリコンからなる活性層20、および支持基板用半導体ウェーハ10に成膜された一部のシリコン酸化膜12bが除去されて支持基板半導体11が露出した半導体露出部13を備える。

(もっと読む)

半導体基板の解析方法

【課題】表面にDZを有する半導体基板において、該DZの有無を判定することを目的の一とする。

【解決手段】表面にDZ、内部にIG層を有する半導体基板において、表面再結合速度を1×104cm/sec以上に調整した第1のサンプルの一次モードのライフタイムτ11を測定し、一次モードのライフタイムτ11および下記数式を用いて、IG層のバルクライフタイムτIGを求め、第1のサンプルに対して、表面再結合速度を1×102cm/sec以下に調整した第2のサンプルの一次モードのライフタイムτ12を測定し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGを比較し、一次モードのライフタイムτ12とIG層のバルクライフタイムτIGの差が0となったとき、DZが消失したと判定することができる。 (もっと読む)

(もっと読む)

1 - 10 / 2,168

[ Back to top ]