国際特許分類[H01L29/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759)

国際特許分類[H01L29/00]の下位に属する分類

国際特許分類[H01L29/00]に分類される特許

101 - 110 / 123

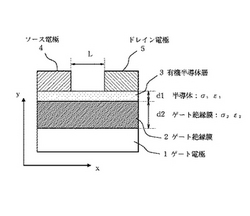

トランジスタのシミュレーション方法及びシミュレーション装置

【課題】構造的な乱れや不純物の存在による状態密度の変化等の影響を受ける、非晶質トランジスタを、精度よくシミュレーションを行う方法を提供する。

【解決手段】半導体層とゲート絶縁層の界面の蓄積電荷を、半導体層とゲート絶縁層を誘電体とした二層積層構造における電圧印加時の界面の蓄積電荷とみなして求める第1の工程と、前記界面の蓄積電荷を基に、前記ソース電極とドレイン電極の間に流れる電流を求める第2の工程と、前記ソース電極及びドレイン電極から前記半導体層に注入される電荷を求める第3の工程と、前記半導体層に内在する電荷を求める第4の工程と、前記第3及び第4の工程で導出した電荷を基に半導体層の伝導率を求める第5の工程と、前記第2の工程で求めた電流の式に第5の工程で求めた伝導率を導入することによりトランジスタ特性を算出する第6の工程とを有する回路のシミュレーション方法。

(もっと読む)

半導体装置の検証方法および回路検証装置

【課題】 ESD保護回路を正確に、または迅速に、もしくは容易に検証することが可能な半導体装置の検証方法および回路検証装置を提供する。

【解決手段】 MOSトランジスタ素子からなるESD保護素子の等価回路として、ノードDとノードSの間に並列に接続されたNMOSトランジスタMN10およびそれに伴う寄生バイポーラトランジスタQN10と、寄生バイポーラトランジスタQN10のベースとノードDおよびノードSの間にそれぞれ設けられた電流源Ifgenおよび電流源Irgenと、寄生バイポーラトランジスタQN10のベースと基板ノードに該当するノードBとの間に設けられた基板抵抗Rsubとを用い、電流源Ifgen,Irgenのモデル式をその演算値が発散しないように変形し、また、このモデル式に電荷の生成および再結合を示す変数を組み込む。

(もっと読む)

パラメータ抽出方法およびパラメータ抽出プログラム

【課題】複数の測定値を再現するシミュレーションに使用されるモデルにおいて、前記モデルに含まれる複数のパラメータを抽出するパラメータ抽出方法を提供する。

【解決手段】パラメータ抽出方法は、誤差ベクトルと、一次勾配行列と、対角二次勾配行列を求める勾配生成工程と、誤差ベクトルと一次勾配行列に基づいて、パラメータを求めるパラメータ生成工程と、対角二次勾配行列に基づいて、一次勾配行列を補正する勾配補正工程と、パラメータ生成工程で求めたパラメータによるモデルに基づくシミュレーションにより、複数のシミュレーション値を得るシミュレーション工程とを有し、パラメータ生成工程と勾配補正工程とを繰り返す第一ループにより、シミュレーション工程に与えるパラメータを決定し、勾配生成工程と、第一ループと、シミュレーション工程とを繰り返す第二ループにより、シミュレーション値を複数の測定値に収束させることを特徴とする。

(もっと読む)

半導体装置設計支援装置、その方法及びプログラム

【課題】 マルチバンドの電子波動関数の固有値を簡単に求めることができる半導体装置設計支援装置を提供する。

【解決手段】 量子井戸構成層をN個のノードによって微小領域に分割する微小領域分割部4と、波数を決定し、決定した波数において有効質量近似されたハミルトニアンを算出するハミルトニアン算出部5と、ノードにおいて、ハミルトニアンの固有関数の取る関数値を求め、隣接するノード間での前記関数値の差分によって固有関数を展開する関数値算出部6、差分変換部7、マトリクス展開部8と、展開された固有関数の固有値を算出し、前記波数でのエネルギーバンドを特定する固有値算出部9とを有している。量子井戸構造の電子エネルギー準位を簡単に求めることができ、量子井戸構造のエネルギーバンド構造を特定し、半導体装置の設計を支援することができる。

(もっと読む)

半導体集積回路の回路シミュレーション方法及び装置

【課題】 高耐圧MOSトランジスタを含む半導体集積回路のシミュレーション精度を向上できる回路シミュレーション方法及び装置を提供する。

【解決手段】 高耐圧MOSトランジスタについてのパラメータモデル(BSIM3モデル)として、ゲート幅範囲を複数に分割し、各分割範囲毎に、その分割範囲に属する高耐圧MOSトランジスタの電流電圧特性を表現したパラメータモデルを用意しておき、シミュレーション対象の半導体集積回路に含まれている高耐圧MOSトランジスタのゲート幅に応じ、複数のパラメータモデルから適用するものを選択して、シミュレーションを行う。

(もっと読む)

半導体集積回路のシミュレーション方法

【課題】抵抗素子の特性を正確に反映できると共に、それぞれ異なる長さ(L)および幅(W)を有する多様な抵抗素子に共通に適用でき、かつ正確度が高くなるようにする。

【解決手段】多様な長さ(L)と幅(W)を有するそれぞれの抵抗素子に対して印加される電圧を変化させながら抵抗値を測定する段階と、測定された抵抗値を電圧に対する線形関数で表すことで、抵抗素子の電圧による抵抗変化係数(VCR:Voltage Coefficient Resist)を算出する段階と、VCRを用いて特定の長さと幅を有する抵抗素子の抵抗値を算出する段階とを備える。

(もっと読む)

回路シミュレーション方法および装置

【課題】素子分離用絶縁膜の幅の異なるトランジスタのモデルを作成し、微細化された集積回路の設計に有用な回路シミュレーション装置およびモデル化方法を提供する。

【解決手段】本発明では分離幅依存パラメータ補正手段4において、素子分離用絶縁膜幅依存性を有するパラメータの近似式を作成し、作成した近似式を用いて得られた補正パラメータの値を元のパラメータの値と置き換えることにより、素子分離用絶縁膜幅の異なるトランジスタのトランジスタモデルを作成する。これにより、より実測データに近い応力によるトランジスタ特性の変化を考慮に入れた、精度の高い回路シミュレーションが可能となる。

(もっと読む)

半導体装置評価装置、半導体装置の評価方法および半導体評価デバイスのシミュレータ

【課題】 半導体デバイスに対する熱ストレス耐性を、従来評価技術に対してより正確に評価することを実現する半導体評価装置等を提供する。

【解決手段】 半導体デバイス101を密閉した温度環境に保管する保存炉102と、保存炉102に装填された半導体デバイス101に微少電流の定電流を供給し、予め設定された時間間隔で半導体デバイス101にかかった電圧値、抵抗値および抵抗変動率を計測する計測装置104と、計測装置104の測定時間、電圧値、抵抗値および抵抗変動率をモニタするコンピュータ105とを備える。これにより、従来技術で課題となっていた温度サイクルを回避し、予め設定された計測時間間隔ごとに評価デバイスの劣化進行を正確にモニタでき、熱ストレスを正確に評価することが可能となる。

(もっと読む)

MOS型トランジスタのシミュレーションモデルおよびそれを用いた回路のシミュレーション方法

【課題】ゲート幅の大きいMOS型トランジスタにも適用でき、ゲート幅の異なる複数のMOS型トランジスタのパラメータセットを容易に準備することのできるシミュレーションモデル、およびそれを用いた回路のシミュレーション方法を提供する。

【解決手段】パラメータセットが、前記SPICEに格納された基本シミュレーションモデルのパラメータセットを抽出するパラメータ抽出ソフトにより抽出された基本パラメータセットにおいて、前記MOS型トランジスタのゲート幅に対応して、前記MOS型トランジスタの移動度U0のパラメータ値のみが、前記パラメータ抽出ソフトにより抽出されたパラメータ値から、前記MOS型トランジスタのドレイン−ソース間における電流−電圧特性に合わせて、設定変更されてなるシミュレーションモデルとする。

(もっと読む)

ESD保護回路の構成を決定する方法及びシミュレーション方法

【課題】 ESD回路の構成の決定に要する時間を短縮することにある。

【解決手段】 ESD保護回路で用いられる素子の物理解析(S2)を行なって、素子のパラメータの中でESD保護特性に比較的大きな影響を与えるものをキーパラメータとして抽出し(S4)、キーパラメータを用いてESD保護回路のデバイス・回路混合シミュレーションを行なって、キーパラメータの最適化を行う(S5)。

(もっと読む)

101 - 110 / 123

[ Back to top ]