国際特許分類[H01L29/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759)

国際特許分類[H01L29/00]の下位に属する分類

国際特許分類[H01L29/00]に分類される特許

11 - 20 / 123

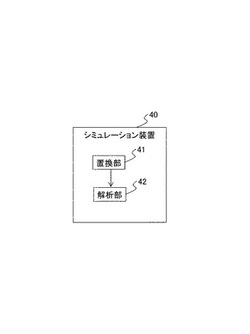

シミュレーション装置、シミュレーション方法及びプログラム

【課題】デバイスシミュレーションにおける解析領域の一部を回路によって置き換えた場合において、電子と正孔の輸送特性の違いを考慮した高精度なシミュレーションを実現すること。

【解決手段】シミュレーション装置は、離散化された偏微分方程式に基づいてデバイスシミュレーションを行うための領域の一部を回路によって置き換える置換部と、当該回路において、第1の回路方程式に基づいて電子電流及び電子ポテンシャルを決定するとともに、第2の回路方程式に基づいて正孔電流及び正孔ポテンシャルを決定する解析部と、を備えている。

(もっと読む)

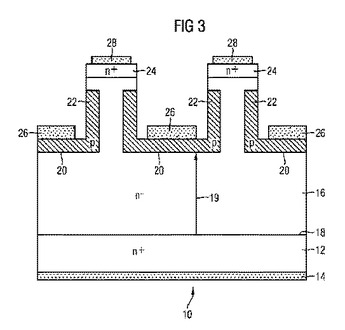

単極半導体部品と半導体装置の製造方法

本発明は、ドリフト層(16)を有する単極半導体部品の製造方法であって、少なくとも1つの広いバンドギャップ材料を含むドリフト層(16)の材料のエピタキシャル析出を手段として、ドリフト層(16)の成長方向(19)に沿って連続的に低下する電荷キャリアドーピング(n)の濃度を有するドリフト層(16)を形成する工程を含む方法に関する。エピタキシャル析出により形成されるドリフト層(16)に炭化ケイ素を使用することにより、下流工程におけるドープ材原子の拡散による電荷キャリアドーピング(n)の連続的に低下する濃度のその後の変化を抑制する。製造方法は特に、単純なおよび/または費用効果的なやり方で、ドリフト層(16)を含む単極半導体部品であって比較的低い順方向損失と比較的高い逆バイアス電圧との有利な比を有する単極半導体部品を実装するために使用されることができる。単極半導体部品は能動半導体部品または受動半導体部品であることができる。本発明はさらに、半導体装置(10)に関する。  (もっと読む)

(もっと読む)

バイポーラ・トランジスタ及びその製造方法

【課題】 バイポーラ・トランジスタ構造体、バイポーラ・トランジスタを設計し製造する方法、及びバイポーラ・トランジスタを有する回路を設計する方法を提供する。

【解決手段】 バイポーラ・トランジスタを設計する方法は、バイポーラ・トランジスタの初期設計を選択するステップ(図25の240)と、バイポーラ・トランジスタの初期設計をスケーリングしてバイポーラ・トランジスタの縮小設計を生成するステップ(245)と、バイポーラ・トランジスタの縮小設計の応力補償が必要かどうかを、スケーリング後のバイポーラ・トランジスタのエミッタの寸法に基づいて判断するステップ(250)と、バイポーラ・トランジスタの縮小設計の応力補償が必要な場合に、縮小設計のトレンチ分離レイアウト・レベルのレイアウトを、縮小設計のエミッタ・レイアウト・レベルのレイアウトに対して調節して(255)バイポーラ・トランジスタの応力補償縮小設計を生成するステップ(260)と、を含む。

(もっと読む)

絶縁ゲート電界効果トランジスタのモデル化方法および集積回路

【課題】絶縁ゲート電界効果トランジスタモデルにおいて内側フリンジ容量を適切にモデル化し、当該モデルを集積回路のシミュレーションに反映し、絶縁ゲート電界効果トランジスタを含む集積回路の設計に使用されるシミュレーション精度を向上する。

【解決手段】ゲート・ドレイン間およびゲート・ソース間の内側フリンジ容量に関する基板電荷Qbfおよびゲート電荷Qgfと、ゲート・ドレイン間の内側フリンジ容量に関わるドレイン電荷Qdfと、ゲート・ソース間の内側フリンジ容量に関わるソース電荷Qsfとを考慮し、QbfがQdfとQsfとQgfとに依存して定義され、さらに、Qgfのドレイン端子バイアスによる偏微分項とQdfのゲート端子バイアスによる偏微分項とが一致し、かつQgfのソース端子バイアスによる偏微分項とQsfのゲート端子バイアスによる偏微分項とが一致するように、QgfとQdfとQsfとQbfとを定式化する。

(もっと読む)

半導体装置の解析方法、設計方法、設計支援プログラム、及び設計支援装置

【課題】トランジスタの高精度な解析及び設計を実現する。

【解決手段】チャネル領域54をチャネル方向(X方向)に離散化した複数の節点56の各々に、予め設定された濃度分布則に従ってチャネル方向(X方向)及び深さ方向(Z方向)の次元を有する不純物濃度N(x,z)を設定するステップと、不純物濃度N(x,z)の深さ方向(Z方向)の次元を削減する次元縮退によって、各節点56における表面ポテンシャルφS0を算出するステップと、各節点56間の相互作用を考慮して表面ポテンシャルφS0を修正するステップと、修正された表面ポテンシャルφSを用いてトランジスタ50の電気的特性を算出するステップと、算出された電気的特性と、予め用意された電気的特性の測定値22とが、所定の範囲内で一致する場合、不純物濃度N(x,z)をトランジスタ50のモデルパラメータ24として記憶装置13に記録するステップとを具備する。

(もっと読む)

モデルパラメータ決定装置、モデルパラメータ決定方法及びプログラム

【課題】半導体集積回路を製造するプロセスを変更した場合において、デバイスモデルによって変更後のプロセスにより製造された半導体素子を表すためにデバイスモデルに含まれるモデルパラメータを容易に決定できるようにする。

【解決手段】モデルパラメータ決定装置は、第1の製法により製造された半導体素子を特徴付ける第1の物理パラメータ群と、半導体素子の特性を表すためのデバイスモデルに含まれるモデルパラメータ群であって第1の製法により製造された半導体素子を表すための第1のモデルパラメータ群と、第2の製法により製造された半導体素子を特徴付ける第2の物理パラメータ群とを入力し、第2の製法により製造された半導体素子の特性を当該デバイスモデルによって表すためのモデルパラメータ群を、第1の物理パラメータ群及び第1のモデルパラメータ群並びに第2の物理パラメータ群に基づいて決定する。

(もっと読む)

少数キャリアダイバータを含む高電圧絶縁ゲートバイポーラトランジスタ

広バンドギャップ半導体バイポーラ接合トランジスタ(「BJT」)と、このBJTのベースに電流を供給するように構成された広バンドギャップ半導体MOSFETとを含む高電力絶縁ゲートバイポーラ接合トランジスタを提供する。これらの素子は、BJTのベース上にあってBJTのエミッタに結合された、BJTのベースの導電型とは逆の導電型を有し、BJTのベースとヘテロ接合を形成する少数キャリア転換半導体層をさらに含む。 (もっと読む)

ばらつきを考慮した半導体集積回路の設計方法

【課題】少数の離散的な電荷によって生じるトランジスタ特性のばらつきを考慮した半導体集積回路の設計方法を提供する。

【解決手段】単一の電荷が付加されることにより生じるトランジスタ特性の変位xの確率密度関数P1(x)を決定する工程と、P1(x)と、付加される電荷の個数nの出現確率と、を元に回路設計上想定すべき設計余裕Mを決定する工程と、を備える。単一の電荷が特性に影響を与えるほど微細なトランジスタを有する半導体集積回路においても、正確にばらつきが計算できる。

(もっと読む)

MOSFETモデル及びそのパラメータ抽出方法

【課題】パワー用途のMOSFETを高精度に模擬できる回路シミュレーション用MOSFETモデルとそのパラメータの抽出を短時間かつ容易に得る。

【解決手段】この発明に係るMOSFETモデルは、MOSFETのSPICEモデルと、前記MOSFETのSPICEモデルの電極端子間に接続した電圧依存性の可変キャパシタからなるMOSFETモデルであって、前記可変キャパシタのうちの前記MOSFETのドレイン―ゲート間の静電容量Cdgは、

前記MOSFETのターンオフのミラー期間における前記MOSFETのドレイン―ソース間の出力電圧Vdsの実測値から抽出して補正する。

(もっと読む)

分子シミュレーション装置

【課題】本発明は、アモルファスの電気伝導度を推定する分子シミュレーション装置を提供することを課題とする。

【解決手段】アモルファスの電気伝導度を推定する分子シミュレーション装置であって、アモルファスに存在する異なる波動関数のキャリアの乗り移り易さ(異なる波動関数のエネルギレベルの差及び異なる波動関数の重なり領域の体積に基づく評価)、空間上の広さ(異なる波動関数の各体積の和から重なり領域の体積を引いた体積に基づく評価)及びキャリアが存在する確率をそれぞれ評価し、当該3つの評価に基づいて電気伝導度を推定することを特徴とする。

(もっと読む)

11 - 20 / 123

[ Back to top ]