国際特許分類[H01L29/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759)

国際特許分類[H01L29/00]の下位に属する分類

国際特許分類[H01L29/00]に分類される特許

81 - 90 / 123

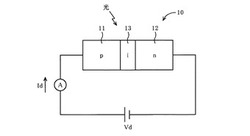

非線形素子の電流電圧特性のフィッティング方法及び電子回路

【課題】非線形素子の電流電圧特性のフィッティング方法において、電圧の範囲によって電流電圧特性が著しく異なる場合にフィッティング精度を向上させる。

【解決手段】測定等により得られた離散的な電流値を第1のステップとして変換関数により離散的な変換値に変換する。第2のステップとして離散的な変換値に対してスプライン関数を用いたフィッティングを実行し、連続的な変換値を与える出力関数を得る。第3のステップとして逆変換関数により、スプライン関数より与えられる連続的な変換値を連続的な電流値に逆変換する。非線形素子に印加される電圧の範囲として、電圧区間A,Bを設定し、それぞれの電圧区間A,Bについて、第2のステップのフィッティングを別々に実行し、電圧区間Aに対応するスプライン関数HA(Vd)、電圧区間Bに対応するスプライン関数HB(Vd)を得る。

(もっと読む)

IBIS補正ツール、IBIS補正方法および波形シミュレーション装置

【課題】例えば波形シミュレーション装置に組み込んで使用することのできるIBIS補正ツールであって、ある特定の電源電圧V0用のIBISデータを、従来よりも高い精度で、所望の電源電圧V1用のIBISデータに補正する。

【解決手段】データ入力部11にて電源電圧V0用のIBISデータをx−y座標の数値データとして読み込み、この数値データと電源電圧V1についてそのx−y座標上での数値データとの相対比(補正係数)を補正係数算出部12で求め、その補正係数に従って電源電圧V1用に補正した補正IBISデータを補正IBISデータ生成部13より得るように構成する。

(もっと読む)

パラメータ抽出方法及び回路動作検証方法並びに当該パラメータ抽出方法を実行させるためのプログラムを具備する記憶媒体

【課題】物理的な意味を有するモデル式におけるパラメータ素子のパラメータ抽出方法において、実測値と計算値の一致の度合いを包括的、且つ定量的に評価することを課題とする。

【解決手段】コンピュータが、モデル式を構成するパラメータの数値を入力するステップと、前記コンピュータが、前記入力されたパラメータの数値を前記モデル式に入力し計算値を算出するステップと、前記コンピュータが、実デバイスの入出力応答を実測値とし、前記実測値と前記計算値の間の一致の度合いの評価を行うステップと、を有し、前記実測値と前記計算値の一致の度合いは、前記実測値の連結線と前記計算値の連結線に挟まれた部分の面積に相当する数値で評価する構成とする。

(もっと読む)

デバイスシミュレーションプログラム

【課題】比較的短い時間でポアソン方程式とシュレディンガ方程式を自己無撞着に解く手段を提供する。

【解決手段】与えられたポテンシャル分布および電子分布を基にポアソン方程式を解いてポテンシャル分布を求め、このポテンシャル分布が収束した場合に、収束したポテンシャル分布を基にシュレディンガ方程式を解いて電子分布を求め、この電子分布を基に演算したシュレディンガ方程式による電子密度と、収束したポテンシャル分布を基に演算したポアソン方程式による電子密度との差を基に電子密度の収束を判定し、電子密度が収束しなかった場合に、収束したポテンシャル分布およびシュレディンガ方程式から得られた電子分布をポアソン方程式にフィードバックしてチャネル領域の厚さ方向の電子分布を求める。

(もっと読む)

基板結合等価回路の生成方法

【課題】半導体基板に寄生する基板インピーダンスを介して電気的に結合する基板結合対策として、ガードリング等による、基板結合に対する低減効果を、設計段階で精度よく予測するシミュレーション手法による大規模半導体集積回路における基板結合の等価回路の生成方法を提供する。

【解決手段】基板結合等価回路の生成方法は、半導体集積回路の形成された半導体チップを水平方向にスライスした2個以上の水平部分チップに分割し、それぞれの水平部分チップを抵抗メッシュ近似して基板結合等価回路を導出して、これらの基板結合等価回路を回路ネットリスト上で接続することにより半導体チップ全体の基板結合等価回路を得る。この等価回路を用いて半導体チップ断面方向に強く局所性を持った不純物濃度分布があっても精度劣化しない基板結合による雑音を解析することを可能とする。

(もっと読む)

シミュレーション方法及びその装置、プログラム、記憶媒体

【課題】 有機物質を電子デバイスなどに用いる際の電気的特性を予測する。

【解決手段】 材料の分子の電子状態、分子振動の状態、及び電子と分子振動との相互作用を表現するハミルトニアンを構築し(S60)、このハミルトニアンの固有関数がポーラロン型の波動関数と非ポーラロン型の波動関数とを重ね合わせた波動関数となるように構築した固有値方程式を解き(S70)、得られた固有関数を用いて状態間を遷移する確率を求め(S80)、前記材料の移動度などの電気的特性を予測する(S90)。

(もっと読む)

半導体回路装置、その製造方法及びそのシミュレーション方法

【課題】レイアウト変更によって半導体回路装置を構成するトランジスタの電流駆動能力をPMISトランジスタ及びNMISトランジスタでそれぞれ最適化できるようにする。

【解決手段】半導体回路装置は、半導体基板1に形成された第1の活性領域3及びその上に形成された第1のゲート電極6pを有するPMISトランジスタ40と、第1の活性領域3と間隔をおいて形成された第2の活性領域4及びその上に形成された第2のゲート電極6nを有するNMISトランジスタ50と、第1のゲート電極6pの両側方で且つその側面から所定の距離以内の領域にそれぞれ形成されたダミーゲート10と、MISトランジスタ40、50を覆うように形成された応力を有するライナ膜11とを有している。ダミーパターンは、第2のゲート電極の両側方における所定の距離以内の領域には形成されていない。

(もっと読む)

磁気トンネル接合デバイス用シミュレーション回路

【課題】少なくとも自由層と固定層とを有する磁気トンネル接合(MTJ)デバイスの動作をシミュレートするためのシミュレーション回路が提供される。

【解決手段】シミュレーション回路は、自由層と固定層の磁化をシミュレートするための、従って、データ記録をシミュレートするための閉スイッチループであって、そこでは、この磁化は平行又は反平行状態を含む閉スイッチループと、MTJデバイスの動作領域の第1の象限をシミュレートするための第1の書き込みループと、夫々、動作領域の第2の象限、第3の象限、及び第4の象限をシミュレートするための第2の書き込みループ、第3の書き込みループ、及び第4の書き込みループと、ビット線の配線抵抗をシミュレートするための第1の抵抗器と、書き込みワード線の配線抵抗をシミュレートするための第2の抵抗器と、磁気MTJデバイスの抵抗をシミュレートするための第3の抵抗器と、を含む。

(もっと読む)

シミュレーション装置、シミュレーション方法、シミュレーションプログラム、記録媒体、及び半導体装置

【課題】理論から一貫してデバイスのIV特性を予測でき、特にナノオーダーサイズの微小デバイスの特性予測に好適に用いることができるシミュレーション装置を提供する。

【解決手段】本発明のシミュレーション装置は、前記デバイスの原子構造モデルを作成する原子構造作成部21と、前記原子構造モデルにおける電子構造計算を実行する電子構造計算部22と、前記電子構造に基づき量子効果及び原子構造を反映させて当該デバイスの第1の電流−電圧特性を算出するIV特性計算部23と、前記計算により得られた第1の電流−電圧特性に対して、電圧補正値による補正処理を実行する補正処理部24と、半古典近似法を用いて第2の電流−電圧特性を計算するIV特性計算部25と、前記第1、第2のIV特性を結合する結合処理部26と、を有する。

(もっと読む)

回路シミュレーション方法および回路シミュレーション装置

【課題】トランジスタの特性を高精度に記述できるモデルパラメータを抽出して、高精度回路シミュレーションを行える環境を提供する。

【解決手段】デバイス特性測定データから1次モデルパラメータαを抽出する手段1と、1次モデルパラメータαを用いて第1次の回路シミュレーション処理を行ってデバイスの実際の動作端子電圧条件c1を記録する手段2と、デバイス特性測定データに対して動作端子電圧条件c1において抽出誤差d1を計算をする手段3と、動作端子電圧条件c1でのデバイス特性測定データに対して抽出誤差d1を参照して優先的にフィッティングする最適化された2次モデルパラメータβを抽出する手段4と、2次モデルパラメータβを用いて第2次の回路シミュレーション処理を行う手段5とを備える。実際の動作端子電圧条件でパラメータを最適化し、パラメータ抽出誤差に起因する設計不良を低減できる。

(もっと読む)

81 - 90 / 123

[ Back to top ]