国際特許分類[H01L29/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759)

国際特許分類[H01L29/00]の下位に属する分類

国際特許分類[H01L29/00]に分類される特許

1 - 10 / 123

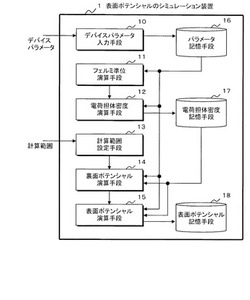

表面ポテンシャルのシミュレーション装置及び表面ポテンシャルのシミュレーションプログラム

【課題】半導体膜中にキャリアを捕獲する欠陥を含む蓄積型の電界効果型薄膜トランジスタについて、表面ポテンシャルを高速かつ高精度に計算する。

【解決手段】シミュレーション装置1は、電気的中性条件に基づいて、フラットバンド条件でのフェルミ準位を算出するフェルミ準位演算手段11と、このフェルミ準位を用いてフラットバンド条件での帯電した欠陥の密度を含む電荷担体密度を算出する電荷担体密度演算手段12と、ポアソン方程式から解析的に導出されるポテンシャルとゲート電圧との間の関係式に、半導体膜中の電荷分布が一定として表面及び裏面ポテンシャルを関連付けた近似式を代入して得た方程式に、電荷担体密度算出手段12で算出した電荷担体密度を代入して裏面ポテンシャルを算出する裏面ポテンシャル演算手段14と、裏面ポテンシャルを前記近似式に代入して表面ポテンシャルを算出する表面ポテンシャル演算手段15とを備える。

(もっと読む)

ESD保護検証装置

【課題】 寄生バイポーラの生成を抑制しつつ、開発遅延を効果的に防止できるESD保護検証装置を提供する。

【解決手段】 回路図データを受け付ける回路図データ取得手段11aと、回路図データから外部端子を抽出する外部端子抽出手段11bと、回路図データからESD保護素子を抽出するESD保護素子抽出手段11cと、寄生バイポーラの発生する可能性のある2つの素子間の関係を規定した第1判定条件に基づき、第1判定条件を満たすESD保護素子を対象素子として設定する第1判定手段11dと、配置配線処理において、寄生バイポーラの発生しないように設定されたレイアウト条件を満たすように対象素子の配置処理を実行して、レイアウトデータを作成するレイアウト作成手段11eと、レイアウトデータを出力するレイアウトデータ出力手段11fと、を備える。

(もっと読む)

絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法

【課題】実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

(もっと読む)

デバイスシミュレーション装置、デバイスシミュレーション方法及びプログラム

【課題】キャリアの速度オーバーシュート効果を考慮した短チャネルトランジスタの電気特性を、高精度かつ数値的に安定に計算できるようにすること。

【解決手段】デバイスシミュレーション装置は、ドリフト拡散モデルとポアソン方程式に基づいてキャリアの電流密度及び静電ポテンシャルを算出するデバイス特性算出部と、キャリアのエネルギー保存式において熱伝導による拡散項を無視するとともに電流密度を一定としたものをチャネルに垂直な方向について積分した式に、電流密度及び静電ポテンシャルを代入して、局所的なキャリア温度を算出する温度算出部と、所定の移動度モデルにキャリア温度を代入して、局所的なキャリア移動度を算出する移動度算出部と、アインシュタインの関係式にキャリア移動度を代入して、局所的なキャリア拡散定数を算出する拡散定数算出部と、を有する。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法

【課題】MOSトランジスタの電気的特性を高精度に再現する。

【解決手段】図形情報生成手段と、パラメータ補正量計算手段と、回路シミュレーション手段とを備える回路シミュレーション装置によって以下の方法で、回路シミュレーションを行う。その方法は、チャネル領域とSTI領域との境界における、チャネル長方向の中点を特定する。そして、ゲート幅方向を縦方向とし、その中点を原点としてそのMOSトランジスタとそのMOSトランジスタの隣の拡散層との距離を縦方向隣接拡散層距離とするとき、その縦方向隣接拡散層距離を、そのチャネル長方向の位置Xに応じて変化する縦方向の距離の関数として特定する。その縦方向隣接拡散層距離の関数と重み付け関数とを掛け合わせた乗算式を生成し、その乗算式に基づいて、パラメータ補正量を算出する。

(もっと読む)

設計支援装置、設計支援方法及び設計支援プログラム

【課題】複数のゲートが同一の拡散領域内に並列に配置されている場合において、トランジスタにおける、機械的応力による移動度の変動を見積もることを目的とする。

【解決手段】開示の装置は、回路データ生成手段と、パラメータ決定手段と、を備える。回路データ生成手段は、半導体集積回路における回路素子のレイアウト情報を基に、当該回路素子の物理特性を反映した回路データを生成する。パラメータ決定手段は、同一の拡散領域内に複数のゲートが設けられている場合において、ゲート電極として機能するゲートを有するトランジスタにかかる機械的応力に関するパラメータを、複数のゲートのレイアウト形状に応じて一意に決定する。ここで、回路データ生成手段は、当該パラメータを用いて、トランジスタにおける、機械的応力の影響を反映した移動度を求め、求められた移動度を回路データに反映する。

(もっと読む)

MOSトランジスタのシミュレーションパラメータの抽出方法

【課題】ゲートとドレインとの重なり部分の容量であるゲートオーバーラップ容量を精度よく抽出する。

【解決手段】本発明の一態様に係るシミュレーションパラメータの抽出方法は、コンタクトプラグ数のみが異なる複数のレイアウトパターンのそれぞれについて、所定のバイアス電圧下におけるゲート−ドレイン間の容量を測定して真のゲートオーバーラップ容量を含む測定値を求め、コンタクトプラグとゲートとの間の寄生容量を求めるためのモデルパラメータを変化させてシミュレーションを行って得られるコンタクトプラグとゲートとの間のコンタクト寄生容量を測定値から減算することによりゲートオーバーラップ容量演算値を求め、当該ゲートオーバーラップ容量演算値がコンタクトプラグの数によらず略一定となるモデルパラメータにおける当該ゲートオーバーラップ容量演算値を真のゲートオーバーラップ容量として抽出する。

(もっと読む)

ヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータ

【課題】パラメータが物理的な意味をもち、容易に初期値の抽出やデバイス開発へのフィードバックが可能で、電気特性を精度良く表現できるヘテロ接合電界効果トランジスタの等価回路モデルの作成方法および回路シミュレータを提供する。

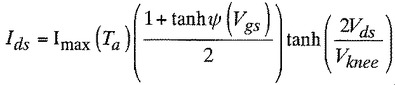

【解決手段】ヘテロ接合電界効果トランジスタのドレイン・ソース間の電流Idsを表現する、次式で定義された、

非線形ドレイン電流モデルを含む等価回路モデルを準備するステップST102と、前記等価回路モデル内のパラメータのうち、Imax、Vknee、gm、Vp、P2、P3、TcImaxをフィッティングパラメータとし、フィッティングにより値を定めるフィッティングステップとを備える。

(もっと読む)

SPICEコーナーモデル作成方法及び装置

【課題】MOSFETのSPICEコーナーモデルの作成方法に関し、電気特性のバラツキの方向が逆方向となる場合のコーナーモデルの作成方法を提供する。

【解決手段】N種類のMOSFETから2種類のMOSFETを取り出す任意の組合せに関し、2種類のMOSFETのバラツキの方向が逆方向の場合のバラツキの大きさの比率Xの表を用意し(S11〜13)、2種類のMOSFETの組合せが指定された場合、比率Xの表から、指定された組合せに対応する比率Xの値を読み出し(S14)、比率Xの値を、2種類のMOSFETのうちの第1のMOSFETのFAST側コーナーと第2のMOSFETのSLOW側コーナーに適用した第1のコーナーモデルと、比率Xの値を、第1のMOSFETのSLOW側コーナーと第2のMOSFETのFAST側コーナーに適用した第2のコーナーモデルと、の2種類の逆方向バラツキのコーナーモデルを構成する(S15)。

(もっと読む)

半導体装置の耐圧シミュレーション方法およびシミュレーション装置

【課題】シミュレータの解析領域を縮小した場合であっても計算結果を保証し得る半導体装置の耐圧シミュレーション方法およびかかるシミュレーション方法を実行するシミュレーション装置を提供する。

【解決手段】

半導体装置に含まれるn型領域およびp型領域と同一の不純物濃度を有するnpn構造若しくはpnp構造を含む接合構造に対して一次元シミュレーションを行って、半導体装置における空乏層についての一次元シミュレーション値を取得する。少なくとも1つのpnジャンクションを含む半導体装置の一部である対象領域について、一次元シミュレーション値を用いて多次元シミュレーションを行って、対象領域内のpnジャンクションを逆バイアスしたときの対象領域内部における一次元シミュレーション値に基づく空乏層のエッジ位置を算出する。空乏層のエッジ位置が対象領域内の所定位置に達したときの対象領域への印加電圧を半導体装置の耐圧と推定する。

(もっと読む)

1 - 10 / 123

[ Back to top ]