国際特許分類[H01L29/40]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931)

国際特許分類[H01L29/40]の下位に属する分類

その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

構成材料に特徴のあるもの (3,446)

国際特許分類[H01L29/40]に分類される特許

1 - 10 / 10

半導体素子の製造方法

【課題】本発明は、歩留まりを向上できる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体素子の製造方法は、半導体基板上に第1の絶縁膜を形成する工程と、前記第1の絶縁膜の一部をエッチングして複数段の段部を形成する工程と、前記第1の絶縁膜上に前記段部を覆うように導電層を形成する工程と、前記導電層の前記段部を覆う部分をエッチングする工程と、を備えることを特徴とするものである。

(もっと読む)

光学装置および光学装置の製造方法

【課題】より効率良く光学装置を製造できる光学装置の製造方法を提供すること。

【解決手段】 複数の光学素子1を備える光学素子シート6を、配線パターン3が形成された基板シート7に接合する工程と、上記接合する工程の後に、光学素子シート6を切断することにより、複数の光学素子1どうしを分離する工程と、上記接合する工程の後に、基板シート7を切断することにより、光学素子1と接合している配線基板を形成する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

太陽電池素子及びその製造方法

【課題】 BSF効果とパッシベーション効果を簡単な構造で実現可能な太陽電池素子を提供する。

【解決手段】 半導体基板1の裏面側全体をBSF層2で覆い、このBSF層2の裏面側一部のみと第一裏面電極4とを接触させ、これらの接触部分4aを除いた裏面側大部分をパッシベーション膜3で覆うことにより、半導体基板1の裏面側大部分における表面再結合損失が低減して太陽電池の性能が向上し、更にパッシベーション膜の裏面側を、上記第一裏面電極4よりも低抵抗な第二裏面電極5で覆うと共に、これら第一裏面電極4と第二裏面電極5とを接触させることにより、第一裏面電極4に比べ低抵抗な第二裏面電極5で抵抗による電力損失が低減され、しかも表面から裏面に到達した長波長の光が第二裏面電極5で半導体基板1の内部に反射して発電効果が向上する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート絶縁膜の信頼性が高く、かつ、チャネル長が充分に確保された半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1に設けられてなる溝21と、ゲート絶縁膜22を介して溝21に形成されたゲート電極25と、溝21の近傍に形成された拡散層26とが少なくとも備えられ、溝21が、半導体基板1の一面上に位置する開口部21aと、断面輪郭線が略円弧状である凹曲面部21cと、凹曲面部21cと開口部21aとを連結する連結曲面部21dとから構成され、連結曲面部21dと凹曲面部21cとの間に稜線部が介在することなく両曲面部21c、21dが連続した曲面で一体化されてなるトレンチゲートトランジスタTrを採用する。

(もっと読む)

窒化物半導体素子

【課題】

窒化物半導体層との接触抵抗のみならずパッド電極との接触抵抗も低く、且つ密着性や機械的強度に極めて優れている窒化物半導体素子を提供することを目的とする。

【解決手段】

本発明の窒化物半導体素子は、第1導電型半導体層、活性層及び第2導電型半導体層が順に積層された積層半導体層と、前記第2導電型半導体層の上面に形成された電極と、を備える窒化物半導体素子であって、前記電極は、少なくとも前記積層半導体層側から第1金属層、第2金属層、第3金属層を順に積層しており、前記第1金属層と第3金属層とは、同一材料を含有する金属層であって、第1金属層は第3金属層よりも密度が高いものであり、前記第2金属層は、前記第1金属層及び第3金属層とは異なる材料を含有している。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート空乏化が抑制され、より簡易な工程で製造することができる半導体装置を提供する

【解決手段】 本発明の半導体装置は、

半導体層10と、

前記半導体層10に設けられた絶縁ゲート電界効果型トランジスタ20と、を含み、

前記絶縁ゲート電界効果型トランジスタ20は、

前記半導体層10の上方に設けられたゲート絶縁層22と、

前記ゲート絶縁層22の上方に設けられ、ゲート電極となる電極層24と、

前記半導体層10に設けられ、ソース領域またはドレイン領域となる不純物領域28と、を含み、

前記電極層24の平均結晶粒径は、30nm以上、500nm以下であり、該電極層24の全体に不純物が分散している

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダミーパターンの面積を大きくしなくても、半導体素子や配線へのプラズマチャージ量を少なくする。

【解決手段】 半導体基板1にトランジスタ11を形成すると共に、半導体基板1上にMNOS素子10を形成する。MNOS素子10に電荷を蓄積した後、層間絶縁膜20を形成する。層間絶縁膜20に、ゲート電極5b上に位置する第1の接続孔20b、及びMNOS素子10上に位置する第2の接続孔20aを形成する。層間絶縁膜20上に、第1の接続孔20bを介してゲート電極5bに接続する配線22bを形成すると共に、第2の接続孔20aを介してMNOS素子10に接続するダミーパターン22aを形成する。

(もっと読む)

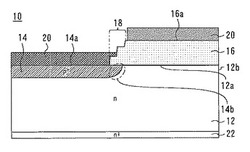

薄膜トランジスタの製造方法

【目的】 i型半導体膜にダメージを与えることなくn型半導体膜を分離でき、かつ、ゲート絶縁膜のピンホール欠陥の発生、およびi型半導体膜とブロッキング膜との界面でのシリサイドの生成を防止する。

【構成】 ゲート電極12を形成した基板11の上に、ゲート絶縁膜13とi型半導体膜14とを順次成膜し、i型半導体膜14の表面に、酸化剤溶液を用いて薄い酸化層14′を形成し、この酸化層14′の上に、a−Siとのエッチング選択比が大きい金属からなるブロッキング膜15を成膜し、このブロッキング膜15をパターニングし、かつその周囲の酸化層14′を除去した後に、n型半導体膜16とソース,ドレイン電極用金属膜17とを順次成膜し、前記金属膜17をパターニングしてソース電極17Sとドレイン電極17Dとを形成し、n型半導体膜16をソース,ドレイン電極間において分離し、かつ前記ブロッキング膜15のソース,ドレイン電極間の部分を除去する。

(もっと読む)

薄膜トランジスタの製造方法

1 - 10 / 10

[ Back to top ]