国際特許分類[H01L29/41]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 電極 (8,931) | その形状,相対的大きさまたは配置に特徴のあるもの (5,475)

国際特許分類[H01L29/41]の下位に属する分類

整流,増幅またはスイッチされる電流を流すもの (1,983)

整流,増幅またはスイッチされる電流を流さないもの (2,575)

国際特許分類[H01L29/41]に分類される特許

1 - 10 / 917

ヘテロ接合電界効果型トランジスタおよびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

太陽電池電極用ペースト組成物

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

電界効果トランジスタ

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

化合物半導体装置及びその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

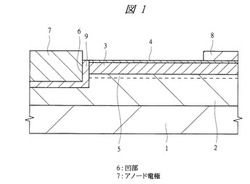

窒化物半導体ダイオード

【課題】高耐圧、低逆方向リーク電流特性を有する二次元電子ガスを導電層とした性能の高い窒化物半導体ダイオードを提供する。

【解決手段】窒化物半導体積層膜の上面に塩素ガスを用いたドライエッチングにより形成した凹部6の底面および側面部に対して、所望の不純物を拡散させる、または所望の不純物を添加した窒化物半導体を再成長することにより、アノード電極7が接触する窒化物半導体積層膜の側面部を高抵抗化させ、逆方向リーク電流を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

電力用半導体装置およびその製造方法

【課題】フィールドプレート電極を有するトレンチゲート構造を備えた電力用半導体装置においてゲート−ソース間容量を低減する。

【解決手段】電力用半導体装置は、第1導電形の第1の半導体層2、フィールド絶縁膜6、フィールドプレート電極7、第1の絶縁膜8、導電体9、第2の絶縁膜11、ゲート絶縁膜10、及びゲート電極12を備える。フィールドプレート電極7は、フィールド絶縁膜6を介して第1の半導体層2のトレンチ5内に設けられる。第1の絶縁膜8は、フィールドプレート電極7上に設けられ、フィールド絶縁膜6とともにフィールドプレート電極7を取り囲む。導電体9は、第1の絶縁膜8上に設けられ、フィールドプレート電極7とは絶縁される。ゲート電極12は、フィールド絶縁膜6の上端上に設けられ第2の絶縁膜11を介して導電体に隣接し、ゲート絶縁膜10を介してトレンチ5内に設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度の低下およびパンチスルーの発生が抑制され、かつ効率的に製造することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET1は、{0001}面に対するオフ角が50°以上65°以下である側壁面20Aを有するトレンチ20が形成された基板10と、酸化膜30と、ゲート電極40とを備えている。基板10は、ソース領域14と、ボディ領域13と、ソース領域14との間にボディ領域13を挟むように形成されたドリフト領域12とを含む。ソース領域14およびボディ領域13はイオン注入により形成されている。ボディ領域13においてソース領域14とドリフト領域12との間に挟まれた内部領域13Aの主表面10Aに垂直な方向における厚みは、1μm以下である。ボディ領域13の不純物濃度は、3×1017cm−3以上である。

(もっと読む)

1 - 10 / 917

[ Back to top ]