国際特許分類[H01L29/70]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586)

国際特許分類[H01L29/70]の下位に属する分類

トランジスタ型装置,すなわち,供給される制御信号に連続的に応答できるもの (2,282)

サイリスタ型装置,例.4層再生作用をもつもの (302)

国際特許分類[H01L29/70]に分類される特許

1 - 2 / 2

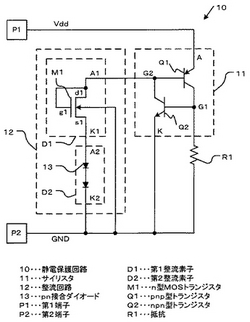

静電保護回路およびそれを用いた半導体集積装置

【課題】 サージおよびラッチアップの両方に対して十分な保護電圧を有し、集積化するのに好適な構造を備えた静電保護回路およびそれを用いた半導体集積装置を提供する。

【解決手段】 アノードAが第1端子P1に接続され、カソードKが第2端子P2に接続されたサイリスタ11と、第1の順方向電圧VF1を有する第1整流素子D1と、第1の順方向電圧VF1と異なる第2の順方向電圧VF2を有する第2整流素子D2とが順方向に直列接続され、サイリスタ11の第2ゲートG2に第1整流素子D1のアノードA1が接続され、サイリスタ11のカソードKに第2整流素子D2のカソードK2が接続された整流回路12とを具備する。

第1および第2の順方向電圧VF1、VF2の組み合わせにより、サイリスタ11のターンオン電圧を微調整する。

(もっと読む)

ESD保護回路

【課題】 面積やコストの増大を生じることなく高いESD耐性を実現することのできるESD保護回路を提供する。

【解決手段】 端子20と接地端子30の間に接続されるESD保護回路1は、3段のダーリントン接続のトランジスタ11〜13と、トランジスタ13のベースと接地端子30間に接続されてトランジスタ13の耐圧を向上させる抵抗14と、トランジスタ13の導通開始電圧調整のために端子20とトランジスタ11のベース間に接続されるダイオード15〜17を有する。端子20へ高電位のESDが入力されるとダーリントン接続されたトランジスタ11〜13が急速に導通し、トランジスタ13が端子20の電荷を接地端子30へ向かって大電流で引き抜く。

(もっと読む)

1 - 2 / 2

[ Back to top ]