国際特許分類[H01L29/744]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | バイポーラ装置 (2,586) | サイリスタ型装置,例.4層再生作用をもつもの (302) | ゲートターンオフサイリスタ (51)

国際特許分類[H01L29/744]の下位に属する分類

電界効果によりターンオフするもの

国際特許分類[H01L29/744]に分類される特許

1 - 10 / 51

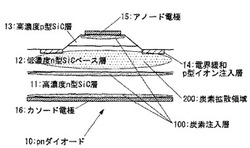

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

バイポーラ半導体素子およびその製造方法

【課題】SiC基板をp型とした結晶品質の良いSiCバイポーラ素子を提供する。

【解決手段】このダイオード素子1によれば、p型のSiCアノード層12,p型のSiCドリフト層13とn+型SiCカソード層14をn型SiC基板21上にエピタキシャル成長により形成してから、n型SiC基板21を除去した。つまり、p型基板に見立てるp+型4H-SiCアノード層12は、エピタキシャル成長により作製するから、バルク成長で作製されるp型基板に比べて結晶成長速度が遅く、p型ドーパントであるアルミニウムの濃度を上げても、結晶品質が良くなる。したがって、この結晶品質が良いp+型4H-SiCアノード層12を基板に見立てることができ、SiC基板をp型とした結晶品質の良いSiCダイオード素子を実現できる。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐電圧特性の温度依存性を改善した半導体装置及び半導体装置の製造方法を提供する。

【解決手段】アノード端子T2に、カソード端子T1に対して大きな電圧を印加したときに形成される空乏層DLに、N型半導体領域N4から到達する電子が増加しないように、N型半導体領域N4を、不純物を高濃度に含む高濃度N型半導体領域N4aと、高濃度N型半導体領域N4aに比較して不純物を低濃度に含む低濃度N型半導体領域N4bとが交互に配置される構成とする。

(もっと読む)

圧接型GTOサイリスタ

【課題】均一なターンオフ動作をさせ、ターンオフ動作の失敗による素子の破壊を抑制可能な圧接型GTOサイリスタを提供することを目的とする。

【解決手段】本発明にかかる圧接型GTOサイリスタは、半導体基体12と半導体基体12上に平面視環状に配置されてカソード電極18を形成するエレメントパターンと、環状の中央近傍において、半導体基体12上に圧接されたゲート電極38と、ゲート電極38の所定方向の側面に接続されたゲートリード44とを備え、環状の中心位置である第1平面中心Aが、ゲート電極38の平面視における中心位置である第2平面中心Bに対し、所定方向にずれて位置する。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

バイポーラ半導体素子

【課題】制御電極による制御能力を向上できるバイポーラ半導体素子を提供する。

【解決手段】このゲートターンオフサイリスタは、隣り合う2列R1,R2のメサ型のアノードエミッタ層5の間で列方向に延在している列間の第1のコンタクトホール20Bに形成された第1のゲート端子15だけでなく、各列R1,R2の端側で各列R1,R2に沿って列方向に延在している端側の第2,第3のコンタクトホール20C,20Dに形成された第2,第3のゲート端子16,17を有する。これにより、列間の第1のゲート端子15と端側の第2,第3のゲート端子16,17とでターンオフ時の転流を分担できて、転流の不揃いを抑制できる。

(もっと読む)

圧接型半導体装置

【課題】外部圧接電極体と半導体基体との間に形成された空間に異物が混入することを防止しつつ、コーティング体の剥がれを防止することができる圧接型半導体装置を提供する。

【解決手段】半導体基体1の主面の一面及び外部圧接電極体の互いの対向面を半導体基体1の外側から囲むように外部圧接電極体の外周面とコーティング体5との間にまたがって配置され、変形することによりコーティング体5にかかる荷重がコーティング体5を半導体基体1から剥がすのに要する荷重以下となる状態を維持した密閉体25を備えた。

(もっと読む)

パワー半導体デバイス

4層npnp構造、カソード面11およびアノード面12があり、ゲート電極4を介してターンオフできるパワー半導体デバイス1。カソード電極2とアノード電極3との間に以下の順で複数の層が配置される。−外側縁によって囲まれ、中央領域がある第1導電型カソード層5、カソード層5はカソード電極2と直接の電気的コンタクトにある,−第2導電型ベース層6,−カソード層5よりも低いドーピング濃度を有する第1導電型ドリフト層7、アノード電極3と電気的コンタクトにある第2導電型アノード層8。ゲート電極4は、カソード面11上にカソード電極2の横に配置され、ベース層6と電気的コンタクトにある。ベース層6は、カソード層5の中央領域に接触している、連続的な層としての、第1の深さに最大ドーピング濃度がある少なくとも1つの第1の層61を具備する。第1の層61よりも高いドーピング濃度を有し、第1の層61とカソード層5との間に配置され、第1の層61のほうを向いているカソード層5の外側縁をカバーする第2導電型抵抗減少層10,10’,10’’、この中でカソード層5の外側縁とベース層6との間の接合での抵抗が低減される。 (もっと読む)

サイリスタ

【課題】サイリスタのサイズを従来と同じにしたままオン電圧VTを低くし、さらに臨界オン電流上昇率di/dtを改善したサイリスタを提供することを目的としている。

【解決手段】サイリスタ100は、表面でアノード電極1に接続されているp型半導体層2の上にp型半導体層101と、p型半導体層101内かつp型半導体層2上面にp型半導体層101より不純物濃度の高いp型半導体層103と、p型半導体層101内かつp型半導体層2上面かつp型半導体層103の間にp型半導体層102より不純物濃度の高いp型半導体層104と、p型半導体層101上面にn型半導体層4と、n型半導体層4内に、p型半導体層6と、p型半導体層6内に、表面でカソード電極8に接続されているn型半導体層7とゲート電極9に接続されているp型半導体層10とを備える。

(もっと読む)

1 - 10 / 51

[ Back to top ]