国際特許分類[H01L29/788]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 整流,増幅,発振またはスイッチングに特に適用される半導体装置であり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁,例.PN接合空乏層またはキャリア集中層,を有するコンデンサーまたは抵抗器;半導体本体または電極の細部(31/00〜47/00,51/05が優先;半導体本体または電極以外の細部23/00;1つの共通基板内または上に形成された複数の固体構成部品からなる装置27/00 (54,759) | 半導体装置の型 (42,689) | 整流,増幅またはスイッチされる電流を流さない電極に電流のみまたは電位のみを与えることにより制御できるもの (37,192) | ユニポーラ装置 (34,588) | 電界効果トランジスタ (34,488) | 絶縁ゲートによって生じる電界効果を有するもの (29,475) | 浮遊ゲートを有するもの (4,374)

国際特許分類[H01L29/788]に分類される特許

71 - 80 / 4,374

半導体装置の製造方法および半導体装置

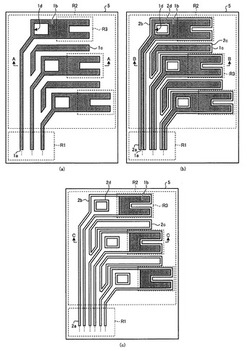

【課題】配線部に比べて引き出し部のスペースが広い場合においても、引き出し部の線幅を配線部の線幅に均一化できるようにする。

【解決手段】側壁パターン2a、2bおよび側壁ダミーパターン2c、2dをマスクとして被加工膜5を加工することにより、側壁パターン2aに対応した配線を下地層4上の配線部R1に形成するとともに、側壁パターン2bに対応した引き出し線5bを下地層4上の引き出し部R2に形成する。この時、下地層4上の引き出し部R2には、側壁ダミーパターン2cに対応したダミー引き出し線5cが引き出し線5bに並列に形成されるとともに、側壁ダミーパターン2dに対応したダミー引き出し線5dが引き出し線5bに並列に形成される。

(もっと読む)

基板処理装置、半導体装置の製造方法及びプログラム

【課題】 酸素含有層を窒素濃度が高い酸窒化層又は窒化層に改質することで、ポリシリコン膜の耐酸化性を向上させる。

【解決手段】 酸素含有層が形成されたポリシリコン膜を有する基板が搬入される処理室と、処理室内に設けられ、基板を加熱する加熱部と、処理室内に窒素及び水素を含む処理ガスを供給するガス供給部と、処理室内に供給された処理ガスを励起する励起部と、加熱部により基板を所定の温度に加熱させ、ガス供給部により供給させた処理ガスを励起部により励起させ、励起した処理ガスを基板に供給させ、酸素含有層を酸窒化層又は窒化層に改質させるように、少なくとも加熱部、ガス供給部及び励起部を制御する制御部と、を備える。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】ジルコニウムを含ませた酸化物半導体材料は結晶化しやすい材料とすることができ、成膜直後において、結晶構造を有する酸化物半導体膜を形成することができる。従って、酸化物半導体膜の成膜後の加熱処理を省略することができるため、量産に適したプロセスである。具体的には、少なくともインジウムと亜鉛を含む酸化物半導体材料に、4族元素の一つであるジルコニウムを含ませる。少なくともインジウムと亜鉛を含む酸化物半導体材料にジルコニウムを含ませた酸化物半導体材料膜(InZrZnOX膜)を提供する。

(もっと読む)

半導体装置の製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置の製造歩留まりを向上させる。

【解決手段】半導体基板1のメモリセル領域に形成された選択ゲート電極CGの上部に酸化シリコン膜24および窒化シリコン膜25を形成した後、メモリマットのゲート長方向の最も外側(ダミーセル領域)に位置する選択ゲート電極CGの上部の酸化シリコン膜24および窒化シリコン膜25を除去することにより、メモリマットの端部を覆う下層レジスト膜12の段差をなだらかにし、下層レジスト膜12の上に形成されるレジスト中間層13の厚さの均一性を向上させ、局所的な薄膜化または消失を防止する。

(もっと読む)

半導体記憶装置

【課題】消費電力を低減出来る半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、選択トランジスタ、メモリセル、ワード線、セレクトゲート線、ドライバ回路12、ロウデコーダ11−0、及び検知回路16を備える。ドライバ回路12は、第1電圧Vss,Vccを出力する。ロウデコーダ11−0内の第1転送トランジスタは、ワード線及びセレクトゲート線の各々に関連付けられ、ドライバ回路12から出力された第1電圧を、ワード線及びセレクトゲート線に転送する。検知回路16は、データの消去時において、ビット線及び/またはソース線に印加される第2電圧を検知して、検知結果に応じてフラグを生成する。ドライバ回路12は、フラグが生成されたことに応答して第1電圧の値を変更して、第1転送トランジスタをカットオフさせる。

(もっと読む)

二重層フローティングゲートを備えているEPROMセル

【課題】インクジェットペンコントロールチップの既存の層を利用して製造できるEPROMを提供する。

【解決手段】EPROMセル70は、ソース領域及びドレイン領域を有する半導体基板52と、第1の金属層60と電気的に相互接続されている半導体ポリシリコン層56を含むフローティングゲート72と、第2の金属層64を含むコントロールゲートとを備えている。フローティングゲート72は、ソース領域及びドレイン領域に隣接して配置され、第1の誘電体層54によって半導体基板52から分離され、コントロールゲートの第2の金属層64は、第1の金属層60との間にある第2の誘電体層62を介して、第1の金属層60と容量結合されている。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

71 - 80 / 4,374

[ Back to top ]