国際特許分類[H01L43/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電流磁気効果またはこれに類似な磁気効果を利用した装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (4,179) | 細部 (155)

国際特許分類[H01L43/02]の下位に属する分類

ホール効果装置のもの (49)

国際特許分類[H01L43/02]に分類される特許

1 - 10 / 106

半導体集積回路およびその動作方法

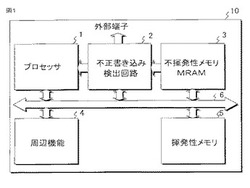

【課題】半導体集積回路の内蔵メモリとしてのMRAMへの不正アクセスに対する保護を改善すること。

【解決手段】半導体集積回路(10)は、プロセッサ(1)と不揮発性メモリ(3)とを具備する。不揮発性メモリ(3)は、複数の磁気ランダムアクセスメモリセルと、複数の磁気リードオンリーメモリセルとを含む。複数の磁気ランダムアクセスメモリセルはプロセッサ(1)による通常書き込みによって書き換えが可能とされ、複数の磁気リードオンリーメモリセルはプロセッサ(1)による通常書き込みによって書き換えが不可能とされる。不揮発性メモリ(3)と接続された感知回路(2)は、不揮発性メモリ(3)の不正アクセスによる複数の磁気リードオンリーメモリセルの状態遷移を感知する。状態遷移に応答して、感知回路(2)は不正アクセスの検出結果をプロセッサ(1)に通知する。

(もっと読む)

磁気センサ

【課題】被実装部材上に回路チップと隣接して搭載される磁気センサにおいて、回路チップとパッドとを電気的に接続するワイヤ同士の接触を抑制することができる磁気センサを提供する。

【解決手段】複数のパッド31〜36を一辺10aと垂直方向において互いに完全にオフセットした状態で配置する。これによれば、被実装部材上に磁気センサの一辺10aを回路チップと隣接して搭載し、パッド31〜36と回路チップとをワイヤで接続した際に、ワイヤ同士が接触してしまうことを抑制することができる。

(もっと読む)

電子部品の実装構造

【課題】実装時における位置ズレが生じる従来の電子部品の実装構造に対して、半田ブリッジの発生を防止しつつ、実装の際に角度ずれが小さいことが要求される電子部品の取り付け角度の精度を高められる電子部品の実装構造を目的とする。

【解決手段】電子部品の実装構造において、電子部品が略直方体形状の基体の側面から複数のリード端子を延出しており、複数のリード端子が基体の四隅の内少なくとも2個所に設けられたアライメント用リード端子とアライメント用リード端子を除く電気的に基体内の電子回路に接続される電極リード端子とからなり、アライメント用リード端子が電極リード端子より長く延出されており、複数の接続ランドがアライメント用リード端子と半田付けされるアライメント用接続ランドと電極リード端子と半田付けされる電極用接続ランドとからなり、アライメント用接続ランドの長さが電極用接続ランドの長さよりも長いことを特徴としている。

(もっと読む)

筐体

【課題】小型化が可能で、部品の搭載、及び部品間の電気的な接続を容易に行うことができる筐体を提供する。

【解決手段】筐体1は、電子部品が搭載される搭載領域27の周囲の高さが搭載領域27の高さ以下であり、配置されたリードフレーム4a及びリードフレーム4bの表面が露出する基部2a、及びリードフレーム4a及びリードフレーム4bの表面の一部が覆われる被覆部2b、を有する第1の筐体2と、第1の筐体2の形状に応じて形成され、第1の筐体2と溶着される溶着部36を有する第2の筐体3と、を備える。

(もっと読む)

半導体素子の検査処理方法

【課題】磁気センサ等の半導体素子の特性検査から梱包までの一連の作業をトレイを使用することなく効率的に行う。

【解決手段】各半導体素子10をダイシングテープ31上でマトリクス状に並べられた状態に分離する工程と、各半導体素子10をダイシングテープ31毎載置して水平方向及び垂直方向に移動しながらプローブに接触させて検査するプローブ検査工程と、プローブ検査工程を経た後の各半導体素子10をダイシングテープ31上から少なくとも1個ずつピックアップして搬送テーブル32上に搭載し、搬送テーブル32により順次搬送される半導体素子10の第1の主面10aを外観検査する第1の主面検査工程と、第1の主面検査工程を経た後の半導体素子10を把持して反転し、半導体素子10の第2の主面10bを外観検査する第2の主面検査工程と、第2の主面検査工程を経た後の半導体素子10を順次ピックアップして梱包する梱包工程とを備える。

(もっと読む)

磁気センサ

【課題】磁気抵抗素子に対するバイアス磁界の強さを確保しつつバイアス磁界の強さのばらつきを抑制して、センサの検出精度を向上させる。

【解決手段】磁気抵抗素子を備えるセンサチップ3を基板2にベアチップ実装することにより、モールドICを用いる従来の磁気センサにおけるモールド成形工程を廃止し、モールド成形に基づくセンサチップ3と磁石5との相対位置のばらつき要因を排除する。また、磁気抵抗素子にバイアス磁界を与える磁石5を基板2に接合することにより、センサチップ3を磁石5に実装する従来の磁気センサと比較して、高導電率の磁石5を用いることが可能になり、磁気抵抗素子に対して強いバイアス磁界を与えることができる。

(もっと読む)

電流センサ

【課題】 低コスト且つ安定した品質で,一方向のリード端子を持つ磁電変換素子を実装基板に対し垂直方向に実装した電流センサを提供する。

【解決手段】 一方向のリード端子を持つ磁電変換素子のリード端子を略直角に折り曲げて素子支持部を形成し、形成した前記素子支持部の先端部を更に実装基板側へ略直角に折り曲げ、実装基板に設けた実装用リード端子挿入孔に挿入して磁電変換素子の実装位置が固定できる位置決め用曲げ部を設けた。

また,磁電変換素子を実装基板に対し垂直方向に実装するため,磁電変換素子のリード端子を略直角に折り曲げて形成した素子支持部の両端を,実装基板面上にハの字状に成形し、磁電変換素子の自立安定性を持たせた。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

センサ装置及びセンサ装置の製造方法

【課題】センシング精度を向上させることのできるセンサ装置を提供する。

【解決手段】このセンサ装置は、リードフレーム30のチップ搭載部31に実装された半導体チップ10を封止した第1の樹脂部材20からリードフレーム30のリード部32a〜32cが導出された半導体パッケージ1を有する。そして、このセンサ装置では、半導体パッケージ1が第2の樹脂部材21によって覆われている。ここでは、リード部32a,32cの第1の樹脂部材20によって覆われていない部分に、リードフレーム30及び半導体パッケージ1のそれぞれの位置決めに利用される貫通孔33a,33bをそれぞれ形成する。

(もっと読む)

磁気抵抗素子を用いた位置検出装置及びこれを用いたレンズ鏡筒

【課題】組立時や落下時に衝撃が加わっても壊れることが無く、簡素な構成で性能を維持できる小型の位置検出装置およびこれを用いたレンズ鏡筒を提供する。

【解決手段】固定部材1と、加圧部材19、配線部材17、及び磁気抵抗素子からなり、固定部材に取り付けられる位置検出装置と、位置検出装置に重畳して設けられ、加圧部材よりも大きい保護部材7と、固定部材に対して回転する回転部材3と、回転部材に取り付けられ、所定のピッチでN,S極が着磁された磁気記録媒体9とを有し、磁気抵抗素子が磁気記録媒体の移動量を検出することで、固定部材に対する回転部材の位置を検出するレンズ鏡筒1であって、磁気抵抗素子の感受面は磁気記録媒体に対向して設けられ、保護部材は加圧部材の輪郭を覆うように配置される構成とした。

(もっと読む)

1 - 10 / 106

[ Back to top ]