国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

21 - 30 / 1,392

半導体装置

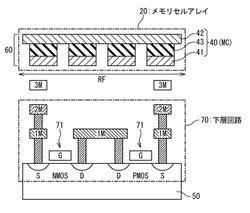

【課題】抵抗変化素子を備える半導体装置(半導体チップ)のチップ面積を削減すること。

【解決手段】半導体装置(1)は、半導体基板(50)上に形成されたトランジスタ(71)を含む下層回路(70)と、半導体基板(50)の上方の配線層(60)に形成されたメモリセルアレイ(20)と、を備える。メモリセルアレイ(20)の各メモリセル(MC)は、配線層(60)に形成された抵抗変化素子(40)を記憶素子として備る。メモリセルアレイ(20)は、メモリセル(MC)の直下に当該メモリセル(MC)との電気的接続用のビアが形成されていない第1領域(RF)を有している。下層回路(70)は、第1領域(RF)の少なくとも一部とオーバーラップするように配置されている。

(もっと読む)

アルミナ抵抗変化型メモリ素子及びその製造方法

【課題】素子駆動電圧、消費電力がともに低く、高安定性・高信頼性・高耐久性かつ、酸素ないしは金属欠損型の金属酸化物層を抵抗変化層に用いる抵抗変化素子形成時のフォーミング処理ないしは欠損への電子注入という動作(フィラメントの形成)を必要としない、金属―絶縁体(抵抗変化層)−金属(MIM)構造の抵抗変化型メモリ素子を提供する。

【解決手段】抵抗変化層に金属ないしは半導体、窒素を添加することにより、あらかじめ伝導パスの一部を形成する(プレフィラメント)ことにより、従来の高電圧フォーミングによるフィラメント形成プロセスを経ることなく、ON電圧と同等レベルの低電圧化することにより、素子駆動電圧、消費電力がともに低く、高安定性・高信頼性・高耐久性の抵抗変化素子。

(もっと読む)

記憶装置及びその製造方法

【課題】信頼性が高い記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る記憶装置は、下部電極層と、前記下部電極層上に設けられた絶縁性の芯材層と、前記芯材層上に設けられ、前記芯材層の側面上には設けられていない上部電極層と、前記芯材層の側面上に設けられ、前記下部電極層及び前記上部電極層に接し、複数の微小導電体が隙間を介して集合した抵抗変化層と、を備える。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】酸素不足度の異なる遷移金属酸化物層を積層して抵抗変化層に用いた不揮発性記憶装置において、素子特性のばらつきを従来よりもさらに抑制する。

【解決手段】第1電極層を形成する工程(A)と、第1電極層の上に酸素不足型の遷移金属酸化物で構成される第1抵抗変化層を形成する工程(B)と、第1抵抗変化層の上端面を液体の酸化剤で化学的に酸化処理して中間酸化層を形成する工程(C)と、中間酸化層をさらに酸化し、第1抵抗変化層の上に第1抵抗変化層を構成する遷移金属酸化物よりも酸素不足度が少ない遷移金属酸化物で構成される第2抵抗変化層を形成する工程(D)と、第2抵抗変化層の上に、第2電極層を形成する工程(E)と、を有する、不揮発性記憶装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】記憶素子の実効面積の減少を抑制する半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法は、基板上に第1導電プラグを形成する工程と、基板上に第1導電プラグの上面を覆う可変抵抗膜を形成する工程と、基板上に第1導電プラグの上面を覆う第1絶縁膜を形成する工程と、第1絶縁膜のうち第1導電プラグ上の部分を除去して、第1絶縁膜に孔部を形成する工程と、第1絶縁膜の上面から孔部内にわたって第1導電膜を形成して孔部内を埋め込むことで、孔部内で可変抵抗膜に接触し、かつ、可変抵抗膜を介して第1導電プラグに電気的に接続するように第1導電膜を形成する工程と、を含む。

(もっと読む)

可変抵抗素子を備える不揮発性メモリセル及び不揮発性半導体記憶装置

【課題】 検知マージンを大きくして可変抵抗素子の抵抗状態をより正しく検知することができ、且つ、面積低減によりコスト抑制を図ることができる不揮発性メモリセル及び不揮発性半導体記憶装置を提供する。

【解決手段】 第1電極と第2電極の間に第1可変抵抗体R1を挟持してなる第1可変抵抗素子RD1と、第3電極と第4電極の間に第2可変抵抗体R2を挟持してなる第2可変抵抗素子RD2と、ドレイン端子が、第2電極と第4電極に、ゲート端子がワードラインに、ソース端子がコモンラインCLに夫々接続されたトランジスタTと、を備え、第1電極材料の仕事関数が第2電極材料の仕事関数より大きい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より小さい値に設定されるか、または、第1電極材料の仕事関数が第2電極材料の仕事関数より小さい値に、第3電極材料の仕事関数が第4電極材料の仕事関数より大きい値に設定される。

(もっと読む)

抵抗変化素子及びそのプログラミング方法

【課題】誤書き込み、及び誤動作を防止し、高信頼化、及び高密度化が可能な抵抗変化素子の提供。

【解決手段】第一の電極(201)と、抵抗変化膜(202)と、第二の電極(203)と、中間絶縁膜(204)と、制御電極(205)と、をこの順に積層した積層構造を備え、前記抵抗変化層(202)と前記中間絶縁膜(204)が直接接していない。

(もっと読む)

不揮発性半導体記憶装置

【課題】非選択メモリセルに流れる逆方向電流を低減させた不揮発性半導体記憶装置を提供することを目的とする。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、複数のメモリセルを有するメモリセルアレイと、選択第1配線に選択第1配線電圧を供給し、非選択第1配線に非選択第1配線電圧を供給する第1配線制御回路と、アクセス対象となるメモリセルに接続された第2配線である選択第2配線に選択第2配線電圧を供給し、その他の第2配線である非選択第2配線に非選択第2配線電圧を供給する第2配線制御回路とを備え、メモリセルは、第1ダイオードのアノード側に第2配線が接続され、第1ダイオードのカソード側に第1配線が接続され、メモリセルアレイは、第2配線制御回路及びメモリセル間の第2配線に挿入され、第2配線制御回路側をアノード、メモリセル側をカソードとする第2ダイオードを有することを特徴とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を劣化させることなく、半導体材料または絶縁膜の結晶特性を改善することができる低温アニールを用いた半導体装置の製造方法、並びに、このような低温アニールに適した半導体装置を提供する。

【解決手段】本実施形態による半導体装置は、半導体基板の上方に設けられた金属からなる下部電極と、下部電極の上方に設けられた金属からなる上部電極と、下部電極と上部電極との間に設けられた結晶層とを備える。下部電極および上部電極の各膜厚は、結晶層の結晶化に用いられるマイクロ波の周波数に対応する表皮効果における表皮層よりも薄い。

(もっと読む)

21 - 30 / 1,392

[ Back to top ]