国際特許分類[H01L45/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 電位障壁または表面障壁をもたず,整流,増幅,発振またはスイッチングに特に適用される固体装置,例.誘電体三極素子;オブシンスキー効果装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,392)

国際特許分類[H01L45/00]の下位に属する分類

固体進行波装置

国際特許分類[H01L45/00]に分類される特許

51 - 60 / 1,392

相変化メモリの形成方法、及び相変化メモリの形成装置

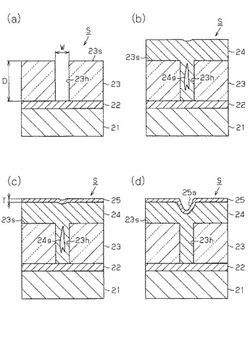

【課題】相変化膜の組成が変わることを抑えつつ、基板の凹部に対する相変化膜の埋め込み性を高めることのできる相変化メモリの形成方法、及び相変化メモリの形成装置を提供する。

【解決手段】相変化メモリの形成に際し、金属カルコゲナイドターゲットをスパッタして絶縁膜23の上面23s及びホール23h内に相変化膜24を形成する。次いで、相変化膜24を覆うキャップ膜25を形成する。更に、相変化膜24を加熱して、相変化膜24によってホール23hを埋め込むリフローを行う。キャップ膜25は、絶縁膜23よりも相変化膜24に対する濡れ性が低い材料で形成される。

(もっと読む)

MIS構造の抵抗変化型メモリ素子

【課題】 従来、オフ電流が大きいため、オフ動作が不安定になることが避けられなかったMIM型ReRAM素子において、電極の片方を金属からp型Si半導体に変更してMIS型にすることにより、10μA以下のオフ電流で安定して動作するReRAM素子を提供する。

【解決手段】 ReRAM素子のオフ動作が、ホットエレクトロン化によるオフ機構による場合は、電子の活性化エネルギーが必要なため、オフ電流が大きくなる問題があった。オフ機構の原理を見直し、活性化エネルギーの必要がない電圧によるpn接合部の空乏化によるオフ機構に変更することにより、極めて低消費電力のReRAM素子を提供することができる。

(もっと読む)

分子メモリ装置の製造方法

【課題】LSIプロセスによって製造可能な分子メモリ装置の製造方法を提供する。

【解決手段】実施形態に係る分子メモリ装置の製造方法は、第1方向に延びる複数本の第1配線を含む第1配線層を形成する工程と、前記第1配線層上に犠牲膜を形成する工程と、前記第1配線層上に、前記第1方向に対して交差した第2方向に延び、前記犠牲膜とは異なる絶縁材料によって形成された複数本の芯材を形成する工程と、前記芯材の側面上に第2配線を形成する工程と、前記犠牲膜における前記第2配線の直下域に相当する部分を除去する工程と、前記第1配線と前記第2配線との間に、メモリ材料となる高分子を埋め込む工程と、前記芯材間であって前記第2配線間の空間に絶縁部材を埋め込む工程と、を備える。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

半導体記憶装置

【課題】記憶素子の加工が容易であり、かつ、記憶素子が安定した特性を有するメモリを提供する。

【解決手段】本実施形態によるメモリは、半導体基板を備える。複数のアクティブエリア列は、半導体基板上に設けられ第1の方向に配列された複数のアクティブエリアをそれぞれが含む複数のアクティブエリア列であり、第1の方向に対して直交する第2の方向に隣接するアクティブエリアは互いに半ピッチずつずれて配置されている。複数のセルトランジスタは、アクティブエリアのそれぞれに対応して設けられている。複数の記憶素子は、複数のセルトランジスタの一端に電気的に接続されている。上部電極は、複数のアクティブエリア列のうち第2の方向に隣接する第1および第2のアクティブエリア列に対応する複数の記憶素子に交互に接続されている。ビット線は、第1および第2のアクティブエリア列に含まれる複数のセルトランジスタの他端に電気的に接続されている。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

相変化メモリ

【課題】三次元構造を有する相変化メモリの熱ディスターブを抑制する。

【解決手段】三次元構造を有する相変化メモリにおいて、選択用MOSトランジスタのゲート絶縁膜として、高い熱伝導率を有する材料を使用し、相変化記録膜からSiチャネル層に伝達する熱を良好にゲート電極に拡散させる。これにより、記録ビットから発生する熱が非選択の隣接ビットに拡散し、隣接ビットのデータを消去する熱ディスターブを抑制する。高い熱伝導率を有するゲート絶縁膜材料としては、BN、Al2O3、AlN、TiO2、Si3N4、ZnOなどを挙げることができる。

(もっと読む)

抵抗変化型メモリデバイスおよびその駆動方法

【課題】リファレンスセルの抵抗状態に応じて、読み出し電流を設定する構成で、誤書き込みによる抵抗の変化が発生することなく、より信頼性の高いリファレンス電流を得ることが可能な抵抗変化型メモリデバイスおよびその駆動方法を提供する。

【解決手段】素子両端に極性の異なる信号を印加することで可逆的に記憶素子の抵抗値が変化するメインメモリセルを含むメモリアレイ部と、素子両端に極性の異なる信号を印加することで可逆的に抵抗値が変化する記憶素子を含み、メインメモリセルのデータを識別するために必要な参照電流を発生させるリファレンスセルを含むリファレンスセル部と、を有し、リファレンスセルの抵抗状態に応じた参照電流の印加電流の向きが設定されている。

(もっと読む)

情報記憶素子

【課題】多値記録が可能で、アモルファスと結晶との相混合比を制御する方式に比較して、パルス電流条件のマージンが広い情報記憶素子を提供する。

【解決手段】相変化材料にそれぞれ形状の異なるパルス電流を流すことによって、アモルファス状態、微細な結晶粒からなる固相結晶、粒径の大きな結晶状態からなる溶融結晶の3状態を形成し、従来に比較してパルス電流条件のマージンが広く、信頼性の高い多値記録が可能な情報記憶素子を実現する。3状態を形成するには、相変化材料の組成を変更したり、他の元素を添加したりすることによって、溶融後の再結晶化速度および抵抗を制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】相変化メモリの書き換え電流および書き換え電圧を低減する。

【解決手段】相変化膜を記憶素子として用いた相変化メモリにおいて、相変化膜2a、2bとして、温度低下に対して結晶化領域の抵抗変化が減少する温度領域を持つ材料を用い、かつ相変化膜2a、2bの間に、相変化膜2a、2bよりも大きい熱伝導率と、相変化膜2a、2bよりも小さい抵抗率を有する中間金属膜1を挿入する。そして、書き換え時に発生する相変化膜2a、2b内の熱を中間金属膜1を通じて放熱することにより、相変化膜2a、2b内の熱分布を均一にすると共に、中間金属膜1近傍の相変化膜2a、2bを局所冷却し、高抵抗状態にすることにより、書き換え電流の過剰な増加を抑制する。

(もっと読む)

51 - 60 / 1,392

[ Back to top ]