国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

51 - 60 / 951

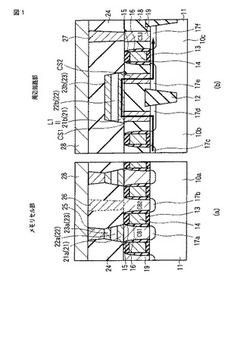

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】抵抗変化型不揮発メモリ装置100は、基板、金属層、下部電極、抵抗変化層、上部電極、及びスペーサー部を備える。金属層(金属密着層142)は、半導体基板102上に設けられる。下部電極144は、金属密着層142上に設けられていて、金属密着層142と接続する。上部電極148は、下部電極144上にあって、下部電極144と対向する位置に設けられている。抵抗変化層146は、下部電極144と上部電極148との間に設けられていて、下部電極144と上部電極148とが重なる領域よりも外側に延在している。スペーサー部150は、抵抗変化層146のうち外側に延在している部分と金属密着層142との間に設けられる。

(もっと読む)

抵抗変化メモリ

【課題】隣接するセル間の電流のリークを防止することができる抵抗変化メモリを提供することを可能にする。

【解決手段】本実施形態による抵抗変化メモリは、第1配線と、前記第1配線と交差する第2配線と、前記第1配線と前記第2配線との交差領域に設けられ、前記第1配線に接続する第1電極と、前記第2配線に接続し、前記第1電極に対向する第2電極と、前記第1電極と前記第2電極との間に設けられた抵抗変化層と、前記第2電極の側部に設けられ、前記第2電極の側部との間に空隙を形成する第1絶縁層および第1半導体層のいずれか一方と、を備えている。

(もっと読む)

抵抗変化メモリおよびその製造方法

【課題】イオン源電極を構成する金属の凝集を防止することができる抵抗変化メモリおよびその製造方法を提供する。

【解決手段】本実施形態の抵抗変化メモリは、第1配線と、第1配線の上方に設けられ第1配線と交差する第2配線と、第2配線の上方に設けられ第2配線と交差する第3配線と、第1配線と第2配線との交差領域に設けられた第1抵抗変化素子であって、第1配線上に設けられた第1抵抗変化層と、第1抵抗変化層上に設けられ第2配線を貫通するとともに第2配線に接続し金属イオン源を含むイオン源電極と、を有する第1抵抗変化素子と、第2配線と第3配線との交差領域に設けられた第2抵抗変化素子であって、イオン源電極上に設けられた第2抵抗変化層を有する第2抵抗変化素子と、を備えている。

(もっと読む)

抵抗変化物質を含む半導体素子及びその製造方法

【課題】抵抗変化物質を含む半導体素子及びその製造方法を提供する。

【解決手段】印加された電圧によって抵抗が変化する抵抗変化物質をチャネル層として含む半導体素子及びその製造方法、前記半導体素子を含む不揮発性メモリ装置に係り、前記半導体素子は、絶縁基板上に配置されたチャネル層、前記チャネル層内に配置されたゲート電極、前記ゲート電極を取り囲むゲート絶縁膜、前記ゲート電極の両側面で、前記チャネル層上に配置されるソース電極及びドレイン電極、並びに前記基板と前記ゲート電極との間に配置される抵抗変化物質層を含み、これにより、前記半導体素子は、スイッチの機能と不揮発性メモリの機能とを同時に遂行することができる。

(もっと読む)

電解質メモリ素子

【課題】 低電圧駆動可能で低消費電力型の不揮発性メモリ素子およびその製造方法を提供する。

【解決手段】 本発明のある態様においては、対向配置された第1基体10Aおよび第2基体20Aと、第1基体および第2基体に挟まれる電解質層30とを備えるメモリ素子1000が提供される。第1基体の基板12の一の面12Sの上には、二酸化バナジウムを主成分とするメモリ層100Aが形成され、メモリ層に接している第1電極部110Aと第2電極部120Aとを有している。第2基体の対向基板22は、第1基体に対向する面の上に第3電極部230Aを有している。そして電解質層30は、第1電極部と第2電極部との間においてメモリ層に近接している。本発明のある態様においては、一方の基体に第1〜第3電極部とメモリ層とが形成された別の典型的なメモリ素子2000も提供される。

(もっと読む)

記憶装置およびその製造方法

【課題】記憶素子の微細化が可能な記憶装置およびその製造方法を提供する。

【解決手段】各々第1電極と第2電極との間に記憶層を有する複数の記憶素子と、ワード線により制御される複数のアクセストランジスタとを備え、前記第1電極は、それぞれ前記アクセストランジスタを介して第1ビット線に接続され、二つの第1電極が、隣り合う異なるアクセストランジスタを介して同一の第1ビット線に接続されていると共に一つの記憶層を共有し、前記一つの記憶層は一本の第2ビット線に接続されている記憶装置。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高集積化に適した不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第3のフィン型積層構造Fin1〜Fin3を有する。第1乃至第3のフィン型積層構造Fin1〜Fin3は、第1の方向に積み重ねられる第1及び第2の半導体層Sm1,Sm2を備える。第1及び第2のアシストゲート電極AG1,AG2は、第3の方向に並んで配置され、第3のフィン型積層構造Fin3の第1の方向にある表面上で互いに分断される。第1のアシストゲートトランジスタAGT1は、第1及び第3のフィン型積層構造Fin1,Fin3内に形成され、第2のアシストゲートトランジスタAGT2は、第2及び第3のフィン型積層構造Fin2,Fin3内に形成される。

(もっと読む)

51 - 60 / 951

[ Back to top ]