国際特許分類[H01L49/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071)

国際特許分類[H01L49/00]の下位に属する分類

薄膜または厚膜装置 (120)

国際特許分類[H01L49/00]に分類される特許

71 - 80 / 951

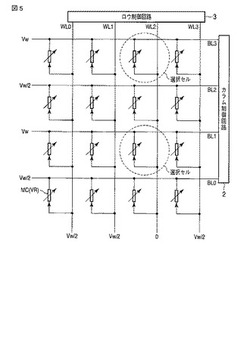

不揮発性半導体記憶装置

【課題】大量データを高速に一括で保存することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】ビット線BL0〜BL3とワード線WL0〜WL3との間に接続され、低抵抗状態から高抵抗状態へ遷移するリセット動作と、リセット動作と異なる極性の電圧を印加することにより高抵抗状態から低抵抗状態へ遷移するセット動作が行われ、リセット動作時に流れるリセット電流がセット動作時に流れるセット電流よりも1桁以上低い可変抵抗素子VRを含むメモリセルMCを複数備えたメモリセルアレイを有する。さらに、メモリセルMCに対してリセット動作及びセット動作を行い、リセット動作を低抵抗状態である第1の複数のメモリセルのうち、選択の第1の配線に接続され、かつ選択の第2の配線に接続される第2の複数のメモリセルに対して一括して行う制御回路を有する。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】 低電圧、低電流で安定したスイッチング動作が可能な可変抵抗素子を実現し、当該可変抵抗素子を備えることで、低消費電力、大容量の不揮発性半導体記憶装置を実現する。

【解決手段】

第1電極12と第2電極14の間に可変抵抗体13を挟持してなる可変抵抗素子2を情報の記憶に用いる不揮発性半導体記憶装置であり、可変抵抗体13を構成する酸化ハフニウム(HfOx)膜または酸化ジルコニウム(ZrOx)膜の酸素濃度が、HfまたはZrに対する酸素の化学量論的組成比xが1.7≦x≦1.97の範囲内にあるように最適化されてなる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】微細化によっても順方向電流が減少することが無いようにする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に形成された第2の配線とを有するセルアレイ層を備え、メモリセルが、電流制御素子、可変抵抗素子及びこれらの間に配置されたシリサイド用金属層を有する。第1の配線又は第1の配線層を形成し、その上に電流制御素子を形成する半導体層、シリサイド用金属層及び可変抵抗素子を形成する可変抵抗素子層を順次形成する。可変抵抗素子層及びシリサイド用金属層を半導体層に達するまで第1のエッチングにより選択的に除去し、少なくとも露出したシリサイド用金属層の側面を覆うように第1の保護層を形成し、選択的に除去した部分に対応する半導体層の部分を第2のエッチングにより選択的に除去し、可変抵抗素子、シリサイド用金属層及び半導体層を覆うように第2の保護層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体記憶装置

【課題】低電圧化を可能にする。

【解決手段】実施形態は、第1の配線と、その上に積層されたメモリセルと、その上に第1の配線と交差するように形成された第2の配線とを有するセルアレイ層を備え、メモリセルが極性の異なる電気信号が印加されることにより電気的書き換えが可能な可変抵抗素子及び可変抵抗素子に双方向の電流を流す電流制御素子を直列に接続してなる。電流制御素子は、i型半導体とその両側に接する第1及び第2導電型半導体とを有する。第2導電型半導体中の第2の不純物の拡散長は第1導電型半導体中の第1の不純物の拡散長より長く、第1導電型半導体とi型半導体との接合部に、第2導電型半導体とi型半導体との接合部よりも多くのインパクトイオンを発生させるインパクトイオン化促進部が形成される。

(もっと読む)

半導体記憶装置

【課題】 長期間のデータ保持特性に優れ、読み出し時のデータの誤り検出および訂正を効率よく行うことのできる半導体記憶装置を実現する。

【解決手段】

金属酸化物を用いた可変抵抗素子を情報の記憶に用いる半導体記憶装置1において、当該可変抵抗素子を高抵抗状態に遷移させる場合に印加する書き換え電圧パルスの電圧振幅を、遷移後の高抵抗状態の抵抗値が時間の経過とともに上昇するデータ保持特性となる電圧範囲内に設定する。具体的には、当該電圧振幅を上昇させるに伴って遷移後の高抵抗状態の抵抗値が所定のピーク値に向って上昇する電圧範囲に設定する。そして、ECC回路106によりデータ誤りが検出された場合、本来低抵抗状態であるべきデータが高抵抗状態に変化したとみなして、誤りが検出された全てのメモリセルの可変抵抗素子を低抵抗状態に書き換え、誤りが検出されたビットを訂正する。

(もっと読む)

不揮発性メモリセル、不揮発性メモリ装置、及び不揮発性メモリ装置の製造方法

【課題】不揮発性メモリセルを提供する。

【解決手段】不揮発性メモリセルは、互いに離隔され順次に積層された第1層間絶縁膜及び第2層間絶縁膜、第1層間絶縁膜と第2層間絶縁膜とを貫く第1電極、第1電極の側面に沿って第1電極と並ぶように形成された抵抗変化膜、及び第1層間絶縁膜と第2層間絶縁膜との間に形成された第2電極を含み、第2電極は金属からなる導電膜と導電膜が含む導電物質の拡散を防止する拡散防止膜を含む。

(もっと読む)

半導体記憶装置

【課題】記憶素子に充分な電流を流すことができるようにセルトランジスタの電流駆動能力を充分に確保しつつ、ユニットセルのレイアウト面積が従来よりも小さい半導体記憶装置を提供する。

【解決手段】本実施形態による半導体記憶装置は、半導体基板と、半導体基板に形成されたアクティブエリアを備える。複数のセルトランジスタがアクティブエリアに形成されている。第1のビット線および第2のビット線は、互いに対をなす。複数のワード線は第1および第2のビット線と交差する。複数の記憶素子の一端がセルトランジスタのソースまたはドレインに電気的に接続され、他端が第1または第2のビット線に接続されている。第1および第2のビット線は、両方とも同一のアクティブエリアに対して記憶素子を介して接続されている。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルを微細化しても、抵抗変化動作に十分な電流を流すことが可能なダイオードを備える抵抗変化型の不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、X方向に延在する第1配線13と、Y方向に延在する第2配線20と、第1配線13と第2配線20との交点に設けられたメモリセル10とを具備する。メモリセル10は、第1配線13上に設けられ一端を第1配線13に接続されたダイオード15と、ダイオード15上方に設けられ一端をダイオード15に直列接続され、他端を第2配線20に接続され、抵抗値の変化で情報を記憶する抵抗変化部19とを備えている。ダイオード15は、第1導電型の第1半導体層13と、第2導電型で、第1半導体層13の内部に伸びている第2半導体層14とを含んでいる。

(もっと読む)

71 - 80 / 951

[ Back to top ]