国際特許分類[H01L49/02]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 27/00〜47/00および51/00に分類されず,他のサブクラスにも分類されない固体装置;それらの装置またはその部品の製造または処理に特に適用される方法または装置 (1,071) | 薄膜または厚膜装置 (120)

国際特許分類[H01L49/02]に分類される特許

1 - 10 / 120

スイッチ素子を有するメモリシステム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置およびその製造方法

【課題】高品質な半導体装置およびその製造方法を提供する。

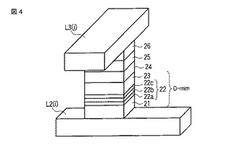

【解決手段】半導体装置は、第1の配線L2(i)と、第1の配線と交差する第2の配線L3(j)と、第1の配線と第2の配線とが交差する各領域に設けられ、一端が第1の配線に接続され、且つ他端が第2の配線に接続され、可変抵抗素子25及び非オーミック素子D−mimが直列接続されたメモリセル構造CUsと、を備え、非オーミック素子は、絶縁層22として、第1の層22aと、第1の層のバンドギャップとは異なるバンドギャップを有し、第1の層上に設けられた第2の層22bと、第2の層のバンドギャップとは異なるバンドギャップを有し、第2の層上に設けられた第3の層22cとを備えている。

(もっと読む)

メモリ素子の駆動方法及びメモリ素子を備える記憶装置

【課題】より安定的にスイッチング動作を行う。

【解決手段】絶縁性基板1と絶縁性基板に設けられた第1電極2及び第2電極3と第1電極と第2電極との間の抵抗値の変化現象を生じる電極間間隙部4とを備えるメモリ素子10に対し、所定の低抵抗状態から所定の高抵抗状態へ移行させるための第1の電圧パルスをパルス発生源から印加し、高抵抗状態から低抵抗状態へ移行させるための第2の電圧パルスの印加を直列接続された抵抗体を介して行うことにより、低抵抗値へ変化後のメモリ素子に流れる電流値を低減させる。

(もっと読む)

抵抗変化メモリ

【課題】非オーミック素子の厚さを薄くする。

【解決手段】本発明の例に係わる抵抗変化メモリは、第1方向に延びる第1の配線と、第2方向に延びる第2の配線と、第1の配線と第2の配線との交点に設けられ、抵抗状態の変化に応じてデータを記憶するメモリ素子20と非オーミック素子30とが直列接続されたセルユニットセルユニットCUと、を具備し、非オーミック素子30Aは、メタル層31と、第1の半導体層33と、半導体層33とメタル層31との間に設けられ、第1のメタル層31との界面に偏在層38bを有する第2の半導体層38とを含む。

(もっと読む)

スイッチング素子

【課題】より単純な構造で構成されるとともに、安定的にスイッチング動作を行うことができる3端子のスイッチング素子を提供する。

【解決手段】絶縁性基板10と、絶縁性基板に設けられた第1電極20及び第2電極30と、第1電極と第2電極との間に設けられ、第1電極と第2電極との間への所定電圧の印加により抵抗のスイッチング現象が生じるナノメートルオーダーの間隙を有する電極間間隙部40と、電極間間隙部に気体の酸素が満たされた状態で少なくとも電極間間隙部を密封する封止部材50とによりスイッチング素子100を構成する。

(もっと読む)

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルの読み出し方法、メモリセルのプログラミング方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法、ならびにコンピュータシステム。

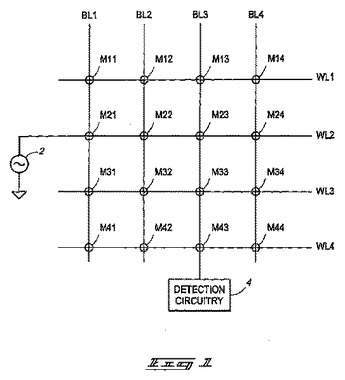

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルを読み出す方法、メモリセルをプログラミングする方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法が記述される。一実施形態においては、クロスポイントメモリセルは、第一の方向に伸長するワード線と、第一の方向とは異なる第二の方向に伸長するビット線とを含み、ビット線およびワード線は、お互いに物理的に接触することなく交差する。クロスポイントメモリセルは、そのように交差する位置でワード線およびビット線の間に形成されるキャパシタを含む。キャパシタは、ワード線からビット線へと流れる直流電流およびビット線からワード線へと流れる直流電流を妨げるように構成された誘電体材料を含む。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】非オーミック性素子と抵抗変化層とを組み合わせたクロスポイント型構成において充分な電流容量を確保し、安定な作動が可能な不揮発性半導体記憶装置を提供する。

【解決手段】下層電極配線15を含む基板11上に形成された層間絶縁層16と、下層電極配線上の層間絶縁層に形成されたコンタクトホールと、下層電極配線15上に形成された非オーミック性素子17と、コンタクトホール中に埋め込まれ、非オーミック性素子17上に形成された抵抗変化層22と、抵抗変化層22と接続し、層間絶縁層16上に形成された上層電極配線23とを備え、非オーミック性素子17は、複数層の半導体層の積層構成、金属電極体層と半導体層との積層構成または金属電極体層と絶縁体層との積層構成のうちの半導体層又は絶縁体層を含む少なくとも1層はコンタクトホールより大きな形状を有し、コンタクトホール中に積層構成のその他の層が埋め込み形成されている。

(もっと読む)

ナノギャップ電極の製造方法

【課題】工程数の少ない手法でギャップ間距離が小さく、さらに様々な電極形状が調製可能であるナノギャップ電極の製造方法を得る。

【解決手段】先端が90度又は鋭角である角を備えた電極材料を基板上に形成し、この電極材料にレーザー光を照射して、鋭角の角の一部を切り離して微小電極を形成すると共に該微小電極と残余の電極本体との間にナノスケールのギャップを形成するナノギャップ電極の製造方法。基板上に10〜100μmのサイズのポリマー又はセラミックスビーズを均一に展開し、この上に電極材料をPVD法又はCVD法により被覆し、このビーズを除去することにより基板上に三角錐の電極材料を残存させ、この三角錐の電極材料にレーザー光を照射し、鋭角の角の一部を切り離して微小電極を形成し、該微小電極と残余の電極本体との間にナノスケールのギャップを形成するナノギャップ電極の製造方法。

(もっと読む)

ショットキーダイオードスイッチおよびそれを含むメモリユニット

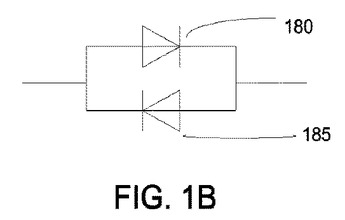

スイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接触部であり、上記第2の接合部と上記第3の接合部はオーミック接触部である。  (もっと読む)

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流層と不揮発性記憶層を有する不揮発性記憶装置で、整流層としてPINダイオードを用いる場合に比して厚さを抑え、整流層のダイオード特性を一様に揃えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するワード線WLと、ワード線WLとは異なる高さに形成され、第2の方向に延在するビット線BLと、ワード線WLとビット線BLとが交差する位置にワード線WLとビット線BLの間に挟持されるように配置される、抵抗変化素子10と整流素子20とを含むメモリセルMCと、を備え、整流素子20は、逆方向電極21、シリコン窒化膜22を含む絶縁膜、金属酸化物半導体からなる金属酸化膜23、および順方向電極24の積層構造を有する。

(もっと読む)

1 - 10 / 120

[ Back to top ]