国際特許分類[H02M3/07]の内容

電気 (1,674,590) | 電力の発電,変換,配電 (135,566) | 交流−交流,交流−直流または直流−直流変換装置,および主要な,または類似の電力供給システムと共に使用するための装置:直流または交流入力−サージ出力変換;そのための制御または調整 (22,926) | 直流入力一直流出力変換 (9,810) | 中間に交流変換をもたないもの (5,345) | 静止型変換器によるもの (5,343) | 抵抗または蓄電器を用いるもの,例.分圧器を用いるもの (799) | 制御電極を有する半導体装置によって交互に充放電されるコンデンサを使用するもの (796)

国際特許分類[H02M3/07]に分類される特許

1 - 10 / 796

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

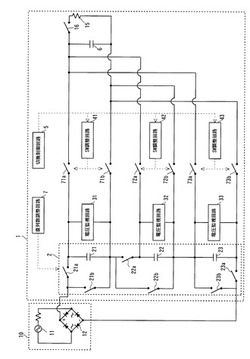

電圧変換回路、および電子機器

【課題】電源回路の出力電圧を負荷回路への供給電圧に降圧する際の電圧変換効率を可及的に好適な状態とする。

【解決手段】電圧変換回路において、電源から充電される複数の一次コンデンサと、前記複数の一次コンデンサのそれぞれに対して並列に接続され、負荷回路への供給電圧で充電可能な二次コンデンサと、複数の一次コンデンサのそれぞれに対応して設けられ、該一次コンデンサと二次コンデンサとの接続状態を切り換える複数のスイッチング回路と、を備える。さらに、電源から複数の一次コンデンサ側への電力供給効率を所定効率に維持するために、該複数の一次コンデンサに含まれる少なくとも一部の一次コンデンサが電源に対して直列接続状態となるように、該電源と該複数の一次コンデンサとの接続状態が調整される。

(もっと読む)

チャージポンプ回路

【課題】天絡などにより出力端子に目標電圧と逆極性の電圧が印加されたときに発生するMOSトランジスタのラッチアップを回避する。

【解決手段】フライングキャパシタCinと出力キャパシタCoutとの間に介挿されたトランスファーMOSトランジスタN1の、バルク端子とグラウンドとの間およびソースとバルク端子との間にそれぞれバルク電圧切り替えMOSトランジスタM1およびM2を設け、出力電圧VOUTが基準電圧Vref1よりも小さければMOSトランジスタM1をオフ、MOSトランジスタM2をオンとして出力電圧VOUTをバルク端子に供給し、出力電圧VOUTが基準電圧Vref1以下であればMOSトランジスタM1をオン、MOSトランジスタM2をオフとしてグラウンド電圧をバルク端子に供給する。

(もっと読む)

チャージポンプ回路及びこれを用いた電源装置

【課題】容易にかつ適切にFETのオン/オフ制御を行う。

【解決手段】チャージポンプ回路1は、キャパシタC1の充放電用スイッチとして用いられるFET103(104)と、FET103(104)に流れる電流またはFET103(104)の両端電圧に応じて検出信号S11(S12)を生成する検出部109(110)と、検出信号S11(S12)に応じてFET103(104)の駆動信号G11(G12)を生成する駆動部107(108)と、を有する。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

チャージポンプ回路およびそれを用いた半導体装置

【課題】起動時の消費電流を小さく抑制できるチャージポンプ回路を提供する。

【解決手段】このチャージポンプ回路30では、ポンプ回路10の起動期間は分周クロック信号CLKDをポンプ回路10に与えてポンプ回路10の電流供給能力を低く設定し、起動期間の終了後はクロック信号CLKをポンプ回路10に与えてポンプ回路10の電流供給能力を高く設定する。したがって、起動期間はポンプ回路10の消費電流を小さく抑制し、起動期間の終了後はポンプ回路10の電流供給能力を高めることができる。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

過電圧保護回路

【課題】外部から供給される直流電圧が低下した場合における電源電圧の低下を抑制するとともに、負荷に対する過電流制限機能を実現する。

【解決手段】主トランジスタT1は、コレクタが直流電源線3に接続される。主トランジスタT1のエミッタおよび直流電源線4を通じて負荷回路6に対して電源電圧Vdが供給される。定電圧回路7は、直流電源線3、4間の直流電圧VBをクランプ値でクランプした定電圧Vaを出力する。昇圧回路8は、電源電圧Vdを昇圧した昇圧電圧Vbを出力する。電圧選択回路9は、定電圧Vaおよび昇圧電圧Vbのうち、高い電圧を主トランジスタT1のベースに与える。昇圧回路は、直流電圧VBがクランプ値以上であるときに昇圧動作を停止する。

(もっと読む)

チャージポンプ及びこれを用いた電源装置

【課題】プリント配線基板上の実装面積削減やコスト削減を実現することのできるチャージポンプを提供する。

【解決手段】チャージポンプ100は、フライングキャパシタ120の充放電用スイッチとして、半導体装置110に集積化されたフローティングNMOSFET111及び112のボディダイオード111d及び112dを用いる。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

1 - 10 / 796

[ Back to top ]