国際特許分類[H03B5/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 細部 (241)

国際特許分類[H03B5/02]の下位に属する分類

国際特許分類[H03B5/02]に分類される特許

1 - 10 / 122

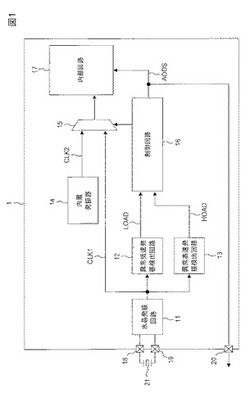

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

発振器

【課題】基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【解決手段】基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、基本波の通過を阻止し、基本波の高次高調波を通過させる周波数選択回路と、を備え、周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、並列経路の共振周波数が、基本波の周波数に設定されている。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

カスケード接続されたエミッタフォロワバッファ段を有する電圧制御発振器

【課題】負荷条件の変化に対しても安定に動作するVCOを提供する。

【解決手段】第1のトランジスタ40aを含む第1のバッファ段と、第2のトランジスタ40bを含む第2のバッファ段とを備え、カスケード接続されたエミッタフォロワバッファ回路として配置されている。トランジスタ40aおよび40bは、VCOコア21を出力から隔離する共通のエミッタ/ソースフォロワ回路に設けられている。したがって結合バッファ段42の両方のバッファ段すなわちトランジスタ40aおよび40bは、同一の電流を分担する。また、これらバッファ段はVCOコア21にACカップリング、逆隔離は直列結合された2つの固有のベース/エミッタ接合キャパシタンスによって決定されるため、キャパシタンスが半分に減少し、これによって、トランジスタ40aおよび40bのサイズが等しければ、2倍の逆隔離が得られる。

(もっと読む)

注入同期発振器

【課題】回路規模を小型化する注入同期発振器を得る。

【解決手段】発振周波数foの注入同期信号を発生する基準発振器1と、注入同期信号を検波し、注入同期信号の高周波電力に応じた直流電圧を発生すると共に発振周波数foの高調波を発生する検波回路2とを備え、検波回路2は、注入同期信号の高周波電力に応じた直流電圧および発振周波数foの高調波を、発振器3を構成するFET8のドレインに供給するので、FET8に注入同期信号を注入する回路と、FET8に直流バイアスを印加するバイアス回路とを検波回路2で共用することができ、注入同期発振器の回路規模を小型化することができる。

また、発振周波数foの高調波をFET8のドレインに供給するので、注入同期発振器として同期を容易にすることができる。

(もっと読む)

発振回路及び発振器

【課題】発振子と発振回路とのインピーダンス整合を容易にとることができる発振回路及び発振器を提供する。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

(もっと読む)

静磁波発振装置の固定構造

【課題】信号線や電源線を経由して伝わる振動を除去するための静磁波発振装置の固定構造を提供する。

【解決手段】永久磁石もしくは電磁石等により加えられた磁界の強さに依存して共振周波数が変化する静磁波素子を用いて所望の発振周波数を得る静磁波発振装置であって、外部と接続する信号線と、前記外部と接続する電源線と、前記静磁波発振装置を実装するための筐体に固定された支持材と、該支持材に固定され前記信号線または前記電源線を固定する緩衝材とを有し、前記信号線や前記電源線を経由して前記静磁波発振装置に伝達される振動を吸収する。

(もっと読む)

高周波発振器

【課題】安定発振、コンパクトなパッケージを実現したSHF帯に好適な高周波発振器を提供する。

【解決手段】低誘電率、低損失の基板材料として水晶板等の耐熱材を最小限の厚さとした基板を主基板2とし、一次実装する能動素子7とIDT3やデスクリート部品8などを主基板2の表裏にそれぞれ配置し、貫通電極6で両面側の間を接続することで配線長を最短とした。LTCCなどの従来の本体基板に代えて薄い水晶等を要部構成部品を実装する主基板とすることにより、薄型化と小型化を実現した。外力・応力に対する脆弱性を、主面側の保護カバーに加えて裏面にも補強カバーを設け、あるいはモールド構造とすることで補強した。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

1 - 10 / 122

[ Back to top ]