国際特許分類[H03B5/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 周波数決定素子が集中定数インダクタンスと集中定数キャパシタンスとからなるもの (396)

国際特許分類[H03B5/08]の下位に属する分類

増幅器の能動素子が真空管であるもの

増幅器の能動素子が半導体装置であるもの (289)

周波数決定素子がブリッジ回路を経て信号が伝送される閉リングに結合されているもの

国際特許分類[H03B5/08]に分類される特許

1 - 10 / 107

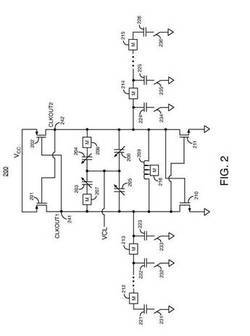

発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

PLL回路及びその制御方法

【課題】回路規模の増大を抑制しつつ、VCOの発振周波数を広い範囲で変化させることができるPLL回路及びその制御方法を提供すること。

【解決手段】本発明にかかるPLL回路1は、VCO11と、制御ロジック14と、位相比較器13と、を備える。VCO11は、両端の電位差に応じて容量値が変化する可変容量素子を有し、電位差に応じた発振周波数の出力信号を出力する。制御ロジック14は、可変容量素子の一端に所定の電圧を印加した状態で、基準信号と出力信号との周波数差に基づいて、当該可変容量素子の他端に印加する制御電圧Vtcを決定する。位相比較器13は、可変容量素子の他端の電圧を制御ロジック14により決定された制御電圧Vtcに固定した状態で、基準信号と出力信号との位相差に基づいて、可変容量素子の一端に印加する制御電圧Vtaを決定する。

(もっと読む)

注入同期発振器

【課題】回路規模を小型化する注入同期発振器を得る。

【解決手段】発振周波数foの注入同期信号を発生する基準発振器1と、注入同期信号を検波し、注入同期信号の高周波電力に応じた直流電圧を発生すると共に発振周波数foの高調波を発生する検波回路2とを備え、検波回路2は、注入同期信号の高周波電力に応じた直流電圧および発振周波数foの高調波を、発振器3を構成するFET8のドレインに供給するので、FET8に注入同期信号を注入する回路と、FET8に直流バイアスを印加するバイアス回路とを検波回路2で共用することができ、注入同期発振器の回路規模を小型化することができる。

また、発振周波数foの高調波をFET8のドレインに供給するので、注入同期発振器として同期を容易にすることができる。

(もっと読む)

電圧制御発振器

【課題】良好な位相雑音特性を有し、かつ広帯域な発振周波数範囲を有する電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器1は、電源と、少なくとも3つのポート10a〜10dを備えるインダクタ11と、少なくとも3つのポートから選択される異なるポート対にそれぞれ接続される少なくとも2つの負性抵抗回路12及び14と、を有し、インダクタは、少なくとも2つの負性抵抗回路に接続されるポート対の間でそれぞれインダクタとして動作可能であることを特徴とする。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

電圧制御発振器

【課題】増幅用のトランジスタに帰還容量成分C1及び結合容量成分C2の直列回路を接続したコルピッツ発振回路を用いた電圧制御発振器において、部品点数の削減に寄与できる技術を提供すること。

【解決手段】トランジスタ21のベースに接続された第1の伝送線路41とトランジスタ21のエミッタとアースとの間に接続された第2の伝送線路42と、を備え、第1の伝送線路41及び第2の伝送線路42を互いに接近させて両者の間に線路間容量成分を形成する。この線路間容量成分を前記帰還容量成分C1として利用すると共に第2の伝送線路42とアースとの間に形成される寄生容量成分を前記結合容量成分C2として利用する

(もっと読む)

VCO利得補償及び位相ノイズ低減のためのプログラマブルバラクタ

【課題】電圧制御発振器の制御利得を発振周波数に対して比較的一定に維持し、位相ノイズを低減したプログラマブルバラクタ装置を提供する。

【解決手段】プログラマブルバラクタ装置100は、複数のデジタルバラクタビットB0、B1、B2によって制御される複数のバイナリ重み付けバラクタ104,106,108を含み得る。プログラマブルバラクタ装置は、複数のバイナリ重み付けバラクタと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとする制御とを含み得る。プログラマブルバラクタ装置の実効容量を変化させる方法は、複数のバイナリ重み付けバラクタを設けることと、プログラマブルバラクタ装置の実効容量を低減するために複数のバイナリ重み付けバラクタの1つまたはそれ以上を選択的にディセーブルとすることとを含み得る。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

1 - 10 / 107

[ Back to top ]