国際特許分類[H03F3/45]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 増幅器 (10,074) | 増幅素子として電子管のみまたは半導体装置のみをもつ増幅器 (6,434) | 差動増幅器 (968)

国際特許分類[H03F3/45]に分類される特許

1 - 10 / 968

全差動型帰還増幅回路および電気機器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

正帰還増幅器およびインターポレーション回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

正帰還増幅器およびインターポレーション回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

制御回路および位相変調器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

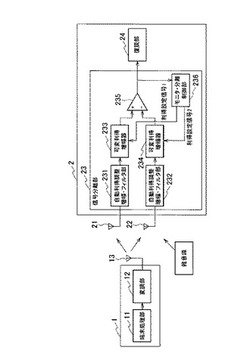

無線通信装置

【課題】雑音の大きな環境下でも安定した通信を可能とする。

【解決手段】アンテナ21,22で受信した信号を利得設定信号1,2で設定される利得で増幅する可変利得増幅器233,234と、可変利得増幅器233,234それぞれの出力信号の差を出力する差動増幅器235と、差動増幅器出力の振幅を検出する振幅モニタ部31と、差動増幅器出力の振幅の変動が最小となる利得設定信号1,2を求める分離制御部32を備える。これにより、アンテナ21,22で受信した信号から雑音を分離し、雑音の大きな環境下でも安定した通信を可能とする通信システムを提供することができる。

(もっと読む)

オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

1 - 10 / 968

[ Back to top ]