国際特許分類[H03H11/46]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 能動素子を用いる回路網 (620) | 1端子対回路網 (64)

国際特許分類[H03H11/46]の下位に属する分類

リアクタンスを擬似するもの (42)

負性抵抗を擬似するもの (1)

国際特許分類[H03H11/46]に分類される特許

1 - 10 / 21

ポジショナ

【課題】低周波のノイズの影響に強いポジショナを提供する。

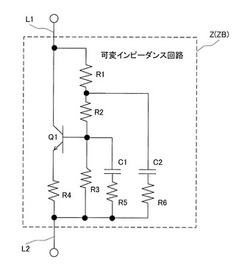

【解決手段】入力ラインL1と出力ラインL2との間に能動負荷Zとして可変インピーダンス回路ZBを設ける。可変インピーダンス回路ZBは、直流の電流信号に対するインピーダンスが低く、交流の電流信号に対するインピーダンスが高いという特性を有し、ラインL1,L2間に接続された抵抗R1とR2とR3との直列回路と、ラインL1にそのコレクタが接続され、そのベースが抵抗R2とR3との接続点に接続されたトランジスタQ1と、トランジスタQ1のエミッタとラインL2との間に接続された抵抗R4と、抵抗R2とR3との接続点にその一端が接続されたコンデンサC1と、コンデンサC1の他端とラインL2との間に接続された抵抗R5と、抵抗R1とR2との接続点にその一端が接続されたコンデンサC2と、コンデンサC2の他端とラインL2との間に接続された抵抗R2とから構成されている。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

デカップリング回路及び半導体集積回路

【課題】容量値の切り換えが可能なデカップリング回路を提供すること。

【解決手段】本発明は、インバータ21を有する。インバータ21は、ゲート電極G1を有するi(iは1以上の整数)個のPMOSトランジスタ及びゲート電極G2を有するj(jは0以上の整数)個のPMOSトランジスタを有する。また、インバータ21は、ゲート電極G3を有するm(mは1以上の整数)個のNMOSトランジスタ及びゲート電極G2を有するn(nは0以上の整数)個のNMOSトランジスタを有する。ゲート電極G1〜G4は、インバータ21の入力端と接続される。ゲート電極G1及びG2の合計面積は、ゲート電極G3及びG4の合計面積と異なる。

(もっと読む)

高インピーダンス回路、フィルタ回路及び増幅回路

【課題】従来技術の高インピーダンス回路は、温度変化等の影響を受けて、高いインピーダンスを維持することができないという問題があった。

【解決手段】本発明にかかる高インピーダンス回路は、ダイオード接続されたトランジスタ21,22を備え、トランジスタ21のバックゲートとトランジスタ22のソースとが接続され、トランジスタ22のバックゲートとトランジスタ21のソースとが接続される。このような回路構成により、温度変化等の影響を抑え、高いインピーダンスを維持することができる。

(もっと読む)

通信システム、車載通信装置及び分岐コネクタ

【課題】電力線を介した通信に関し、利得低下の防止及び伝送品質の低下を防止を実現することができる通信システムを提供する。

【解決手段】バッテリ4からの電力を供給するための電力線3がECU1,1,…及びアクチュエータ2,2,…に接続し、ECU1,1,…及びアクチュエータ2,2,…は夫々電力線3から電力の供給を受けると共に、電力線3を介して通信を行なう。ECU1,1,…及びアクチュエータ2,2,…は、電力線3の分岐点31からの分岐に夫々接続される。分岐点31に、負性インピーダンス変換回路5の一端を接続し、他端を固定電位に接続する。

(もっと読む)

フィルタ回路およびバイアス回路

【課題】回路面積の縮小を図りつつ、出力信号に含まれるオフセットを減少させることが可能なフィルタ回路を提供する。

【解決手段】フィルタ回路は、入力端子と出力端子との間に接続された第1のキャパシタと、前記出力端子と設定電位との間に接続されたバイアス回路と、を備え、前記バイアス回路は、前記出力端子と設定電位との間に接続された第1のMOSトランジスタと、前記第1のMOSトランジスタのゲートと前記出力端子との間に接続された第2のキャパシタと、前記第1のMOSトランジスタのゲートに一端が接続され、第1のバイアス電位が他端に印加された抵抗素子と、を有する。

(もっと読む)

抵抗増倍回路

【課題】チップ面積の増大を招くことなく、半導体材料に起因するhfeのばらつきなどに影響されることのない安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に抵抗器3の一端が接続され、抵抗器3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、抵抗器3の他端に接続されて、信号入力端子8から見た抵抗器3の見かけ上の抵抗値が1/(1+N)倍に見えるものとなっている。

(もっと読む)

容量増倍回路

【課題】半導体材料に起因するhfeのばらつきなどに影響されることなく、安定した増倍率を確保する。

【解決手段】カレントミラー比が共に1:Nに設定された第1及び第2のカレントミラー回路21,22の各々の入力段の間に、第1及び第2のトランジスタ1,13がトーテムポール接続により直列接続されて設けられ、この第1及び第2のトランジスタ1,13の相互の接続点に容量3の一端が接続され、容量3の他端は、入力信号が印加可能とされ、第1及び第2のカレントミラー回路21,22の出力段は、相互に接続されて信号出力可能とされると共に、容量3の他端に接続されて、信号入力端子8から見た容量3の見かけ上の容量値が(1+N)倍に見えるものとなっている。

(もっと読む)

交流直流分離回路

【課題】交流成分に対して比較的高い入力インピーダンスを確保しながらも、従来構成に比べてインダクタの必要数を低減することができる交流直流分離回路を提供する。

【解決手段】ボルテージフォロア回路2は、第1のインダクタL1の一端と基準電位点との間の交流電圧と同振幅且つ同位相の交流電圧を第1のインダクタL1の他端と基準電位点との間に出力する。フィルタ回路3は、第1のインダクタL1の前記他端にコレクタが接続され、第1のインダクタL1の前記他端に抵抗R2を介してベースが接続され、直流出力端子Tdcにエミッタが接続されたトランジスタTr1と、トランジスタTr1のベースと前記基準電位点との間に挿入されたキャパシタC3とを有する。

(もっと読む)

半導体集積回路および装置

【課題】外部抵抗を備える半導体集積回路において、外部抵抗の抵抗値を容易に変更可能にする技術を提供する。

【解決手段】外部抵抗を備える半導体集積回路であって、半導体集積回路の入出力インピーダンスは、外部抵抗の抵抗値に基づいて調整され、外部抵抗は、その抵抗値として、複数の抵抗値の中から所望の抵抗値を選択できるように形成されていることを特徴とする半導体集積回路。

(もっと読む)

1 - 10 / 21

[ Back to top ]