国際特許分類[H03H17/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | ディジタル技術を用いる回路網 (734)

国際特許分類[H03H17/00]の下位に属する分類

周波数選択回路網 (514)

位相推移を与える回路網 (21)

国際特許分類[H03H17/00]に分類される特許

21 - 30 / 199

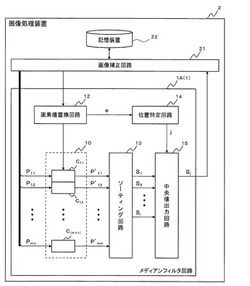

メディアンフィルタ回路

【課題】 複数の大きさのメディアンフィルタを1つの回路で実現でき、画像データの端部の画素についても容易に且つ適切に補正できるメディアンフィルタ回路を提供する。

【解決手段】 画素値を格納するk(k=n×mまたはn×m×r、n、m、rの少なくとも1つは2以上)個のセルCと、無効セルの画素値を、有効セルの画素値の最小値以下または最大値以上の値に置き換える画素値置換回路12と、画素値の大きい順または小さい順に、i番目までのセルCの画素値を順序付けするソーティング回路13と、有効セル数eに基づいて、中央値として用いる画素値の順位jを出力する位置特定回路14と、j番目の順位のセルの画素値を出力する中央値出力回路15と、を備える。

(もっと読む)

振幅制限装置

【課題】電子機器に搭載され、何らかの信号処理の対象となる信号の振幅を既定のしきい値以下に制限する振幅制限装置に関し、構成が複雑化することなく、入力信号の振幅制限を高い精度で安定的に実現できる振幅制限装置を提供する。

【解決手段】しきい値に対する入力信号の瞬時値の超過分を示すパルスの帯域制限によって得られた補正信号を前記入力信号から減じ、前記入力信号の振幅を制限する振幅制限装置であって、前記パルスに先行して前記しきい値に対する前記入力信号の瞬時値の超過分を示す先行パルスを帯域制限し、前記補正信号を予測する予測手段と、前記予測手段によって予測された補正信号の前記パルスの時点における瞬時値と、前記パルスの尖頭値との内、大きい一方を前記補正信号を得る帯域制限の対象とする制御手段とを備える。

(もっと読む)

サンプリング周波数変換装置

【課題】 サンプリング周波数変換のレイテンシ、変換後のデータの周波数ゆらぎを低減する。

【解決手段】 1/Lダウンサンプラ3は、前段からのデータを記憶し、ライト要求信号に応じて最新の所定個数の記憶データからライト要求信号発生時のデータを補間演算し、FIFO4に送る。FIFO4は、ライト要求信号に応じて1/Lダウンサンプラ3からのデータを記憶し、リード要求信号に応じて記憶データを古いものから順に読み出す。ライト速度調整回路6は、周波数制御情報に応じた時間密度でライト要求信号を発生し、1/Lダウンサンプラ3に補間演算を実行させ、結果をFIFO4に記憶させる。速度補正用ポインタ8は、ライト要求信号により増加され、リード要求信号により減少される。ライト速度調整回路6は、速度補正用ポインタ8に基づいて周波数制御情報を補正する。

(もっと読む)

低音増幅回路

【課題】 簡易な構成で低域を増強する。

【解決手段】 LPF41を通過した入力信号は、高周波音発生部42からの帯域外の高周波音が加算器43で加算される。D/A44でアナログに変換された加算器43からの出力はアナログボリューム45で調整され、アナログボリューム45の出力から高周波音の成分をHPF48により抽出する。抽出された高周波音の成分のレベルA’と、加算器43で加算された高周波音のレベルAとのレベル比A’/Aに応じてLPF41における高域の減衰特性を制御する係数を決定する。

(もっと読む)

間引きフィルタおよび間引きプログラム

【課題】標本化の間隔が不均一である場合にも適用可能な間引きフィルタおよび間引きプログラムを提供する。

【解決手段】間引きフィルタ1は、注目する出力標本点P1近傍に存在する複数の出力標本点を順次選択するためのインデックスkを生成する第1計数手段10と、インデックスkに基づき隣接する2つの出力標本点を選択し、選択した2つの出力標本点間を区分として、区分内の整数値を標本点位置xとして順次生成し、標本点位置xを時間方向に正規化して正規化座標vを生成する第2計数手段20と、正規化座標vを基本関数f(x)に代入し、関数値f(v)を生成する関数値生成手段30と、関数値f(v)に2つの出力標本点間の距離の逆数を乗算し、区分ごとのタップ係数h(x)を生成する区分タップ係数生成手段40と、標本点位置xとタップ係数h(x)とに基づき入力標本点に対応するタップ係数を生成するタップ係数生成手段50と、を備える。

(もっと読む)

カスケードフィルタバンクにおけるエイリアシングを削減する方法および装置

【課題】カスケードフィルタバンクにおいて近接するサブバンド間のエイリアシングを削減する方法および装置を提供する。

【解決手段】エイリアス削減フィルタバンクは、第一ステージフィルタバンクのM1サブバンドからの一連のM2サブバンドからの信号をフィルタリングし、加える。次に続く分析フィルタバンクによりエイリアス削減ステージ後に高周波解像度が得られる。これらのサブバンドの信号は最初にエイリアス削減フィルタバンクに供給され、エイリアシングを減じる。第一ステージフィルタバンクがM1バンドを有する変調均一フィルタバンクであり、エイリアス削減のステージがM2バンドを有し、エイリアスキャンセルが可能となる場合、エイリアス削減フィルタバンクは、M1/M2のサンプリングレート比率により基準化された周波数を有するが、第一ステージの合成フィルタバンクと類似する周波数応答を有していなくてはならない。

(もっと読む)

周波数再構成が可能なデジタルフィルタ及びこれを用いたイコライザ

周波数再構成が可能なデジタルフィルタ及びこれを用いたイコライザを開示する。開示するフィルタは、モデルフィルタ応答に対してサンプリング定数によりスケーリングされるアップサンプリングを行い、上記モデルフィルタ応答が一定周期を有して反復されるマルチイメージ応答を生成するためのサンプリングカーネル格納部、上記マルチイメージが生成されていない周波数領域に、上記一定周期を有して反復され、上記マルチイメージと同一の特性を有するマルチコンプリメンタリイメージ応答を生成するためのコンプリメンタリ変換部、及び上記マルチコンプリメンタリイメージ及び上記マルチイメージのうち、選択された帯域に相応するイメージの応答を演算するイメージ応答演算部を含む。極めて少数のパラメータ変更だけで多様な帯域通過特性を有するように周波数再構成が可能であり、使用者が容易にフィルタの帯域を変更できる利点がある。 (もっと読む)

保護制御装置および保護制御方法

【課題】本発明の目的は、高速サンプリングによってアナログフィルタ回路及びディジタルフィルタ回路を小型化すると共に、複数のアナログ入力に対してA/D変換のタイミングを揃えることで保護制御演算の位相誤差をなくすことである。

【解決手段】電力系統からアナログフィルタ11a〜11nを介して入力される複数のアナログ信号個別に、サンプリング周波数に従いディジタルデータに変換するA/D変換手段12a〜12nを複数備え、前記ディジタルデータに対しフィルタ演算を実行するディジタルフィルタ手段200と、前記ディジタルフィルタ手段の演算結果を基に保護制御演算を実行して前記電力系統に対する保護信号を生成する保護制御演算手段を備える。

(もっと読む)

離散時間受信機

【課題】本発明は離散時間受信機に関する。

【解決手段】本発明の離散時間受信機は、サンプリングクロックに応じて入力信号をサンプリングするサンプリングミキサと、制御信号を用いてデシメーション比を調節し、フィルタクロックを用いて上記サンプリングされた信号をフィルタリングする離散時間フィルタと、上記サンプリングミキサに供給されるサンプリングクロックを生成し、上記サンプリングクロックの周波数と予め設定された出力周波数とを比較して制御信号及びフィルタクロックを生成するクロック生成器と、を含み、広帯域の入力信号に対して出力信号のダイナミック範囲を向上させることができる。

(もっと読む)

デシメートされた係数(decimatedcoefficients)のフィルタリングを実行する他の回路またはアクティヴ雑音相殺回路における遅延技術

【解決手段】本開示はデジタル・ドメインのアクティヴ雑音相殺について用いられ得る回路構成が記載されている。特に、本開示は、信号処理についての遅延を用いる他の回路、またはデジタル適応雑音相殺回路の一つまたはそれ以上の望ましい遅延を達成するために、メモリ・ベース遅延回路というよりむしろダウン・サンプル・ユニット及びアップ・サンプル・ユニットの使用を提案する。ダウン・サンプル・ユニット及びアップ・サンプル・ユニットによって達成される遅延は、種々のアクティヴ雑音相殺回路構成について必要な遅延を自由に生成するように調整され得る。多くの適応アクティヴ雑音相殺回路構成が議論され、技術は、低レーテンシー平衡回路のような他のタイプの回路について有効であり得る。 (もっと読む)

21 - 30 / 199

[ Back to top ]