国際特許分類[H03H17/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | ディジタル技術を用いる回路網 (734)

国際特許分類[H03H17/00]の下位に属する分類

周波数選択回路網 (514)

位相推移を与える回路網 (21)

国際特許分類[H03H17/00]に分類される特許

71 - 80 / 199

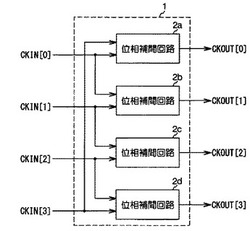

位相差平滑化装置

【課題】多相クロック生成及び伝送の過程において発生した多相クロックの位相誤差を低減する。

【解決手段】入力多相クロックのうち所望の位相関係にある複数のクロックを入力して各クロックの位相に所望の重み付けをする重み付け手段と、重み付けされたクロックを加算する加算手段と、を有する位相フィルタ回路を前記多相クロックの位相数と同数備え、位相フィルタ回路から出力されたクロックを出力多相クロックとして出力する。

(もっと読む)

サンプリングレート変換装置、およびサンプリングレート変換方法

【課題】

小規模の信号処理によって、好適にサンプリングレート変換する。

【解決手段】

デジタル信号のデータを入力し、第1の対称軸を中心に係数値が対称形をなすタップ係数と前記入力データとの畳み込み演算結果を出力する第1の演算部(奇数タップ対称フィルタ)と、第2の対称軸を中心に係数値が対称形をなすタップ係数と前記入力データとの畳み込み演算結果を出力する第2の演算部(偶数タップ対称フィルタ)とを用い、出力データの画素位置と入力データの画素位置の関係から定められる混合比に応じて前記第1および第2の演算部の出力を混合することにより、サンプリングレートが変換された出力データを生成する。

(もっと読む)

ディジタルオーディオアンプ

【課題】入力されたオーディオ信号のレベルに対応して最適のディジタルゲインを設定することができるディジタルオーディオアンプを提供する。

【解決手段】係数乗算部32が、入力されたオーディオ信号に対してゲインパラメータを乗算する。この係数は係数演算部36から供給される。DSP乗加算処理部33がオーディオ信号に対して音場形成などの処理を行い、加算部34が元のオーディオ信号と処理されたオーディオ信号とを加算する。クリップ検出部35はこの加算部34で加算された信号がクリップしているか否かを検出する。この処理を所定のオーディオ信号(例えば1曲の楽曲)について行い、係数演算部36がクリップ検出部35の検出結果に応じてゲインパラメータを決定する。このゲインパラメータが係数乗算部32に設定され、再度所定のオーディオ信号が入力されたとき最適のゲインで再生・録音することができる。

(もっと読む)

周波数変換装置

【課題】FIRフィルタを用いた簡単な処理で音響信号中の任意の周波数成分に任意の周波数変化を与え、また、振幅周波数特性の操作と周波数の操作を同時に実現する。

【解決手段】AD変換部1からのデジタル信号を処理する信号処理部2は、フィルタ部4とフィルタ係数データを蓄えるメモリー部5を有する。フィルタ部4に含まれるFIRフィルタ40とFIRフィルタ41は、1サンプリング周期中にメモリー部5から供給されるデータでフィルタ係数を更新する。それぞれのFIRフィルタの各周波数成分の振幅は時間とともに独立に変動する。振幅変動の周期はFIRフィルタ40とFIRフィルタ41に共通だが、位相が90度異なっている。フィルタ部4は2つのFIRフィルタの出力信号の差または和を出力する。

(もっと読む)

サンプルレート変換システムにおける補間係数を計算するための方法及び装置

本発明によって、サンプルレート変換システムにおいて決定的に重要なパラメータである補間係数を、DSPクロックとデータクロックとの間に複雑な関係があるリアルタイムシステムで計算することを可能にする。通常、このようなシステムにおけるクロックの2つ又は3つは、単純な関係(CLOCK1=2*CLOCK2等)を有する。この関係は、実際には、考慮されるクロックが3つではなく1つ又は2つしかない縮退した場合につながる。さらに、本発明によって、DSPクロックレートよりも高い入力データレートが可能になる。本発明は、任意の時間遅延が出力信号に適用されるようにすることも提供する。 (もっと読む)

フィルタ装置、フィルタ装置のフィルタリング方法およびフィルタリングプログラム

【課題】時系列データに対して、スパイク型ノイズ212を識別し、スパイク型ノイズ212を検出して除去することを目的とする。

【解決手段】分析対象行列生成部120は基準データ220から抽出した複数の基準レコード221と分析対象データ210から抽出した1つの分析対象レコード211とをそれぞれ列にして分析対象行列240を分析対象レコード211毎に生成する。主成分分析部130は各分析対象行列240を主成分分析して各第1主成分係数列ベクトル251から成る第1主成分係数行列260を生成する。ノイズ検出部140は第1主成分係数行列260から抽出した第1主成分係数正方行列261の逆対角成分262の比率ρを算出する。スパイク型ノイズ除去部150は逆対角比ρとノイズ判定閾値ntとの比較によりスパイク型ノイズ212と判定された逆対角成分262に対応する時点の分析対象データ210の計測値を除去する。

(もっと読む)

波形等化器、及び、波形等化器の制御方法

【課題】従来に比べて回路規模の削減を実現する波形等化器を提供する。

【解決手段】フィルタ部11は、直列接続された(k−1)個の遅延器1111〜111k−1からなる遅延器群111を用いて入力信号を1サンプル毎に順次遅延させ、遅延器群111によりm(mは、0≦m≦k−1を満たす自然数。)サンプル分遅延された各入力信号に対して、合計k個の乗算器1120〜112kからなる乗算器群112により、それぞれタップ係数を乗じ、乗算器群112の各乗算器1120〜112kでタップ係数が乗算された各入力信号を加算器113により加算し、係数制御部14は、遅延器群111によりmサンプル分遅延された入力信号に対して乗算するタップ係数の値を、等化誤差推定部13からNサンプル分遅延して出力された誤差信号と、遅延部12から出力される(m+N)サンプル分遅延された入力信号とに基づいて算出する。

(もっと読む)

アップダウンサンプリング装置とアップダウンサンプリング方法、及びそのプログラム

【課題】アップダウンサンプリングの周波数領域における処理量を減らす。

【解決手段】周波数分析部は、入力信号を周波数領域の信号に変換して入力信号周波数スペクトルを出力する。イメージング計算部は、入力信号周波数スペクトルを複写した折り返しスペクトルであるイメージング成分を、所定のUの値に従って生成しイメージング計算後信号周波数スペクトルを出力することで周波数領域での処理量を減少させる。フィルタ乗算部は、イメージング計算後信号周波数スペクトルに周波数領域のフィルタ係数を乗じてイメージング成分とエリアシング成分を抑える。ダウンサンプル部は、フィルタ乗算部の出力信号を入力とし、所定のMの値に従ってエリアシング成分を加算した出力信号周波数スペクトルを出力する。周波数合成部は、出力信号周波数スペクトルをサンプリング周波数UfS/Mで再合成して時間領域の信号に変換して出力する。

(もっと読む)

復調装置

【課題】フルディジタル化による回路規模の増大を抑える。

【解決手段】フィルタ部3に入力する信号の同期点(ベースバンド信号波形の振幅が最大となる点)がタイミング同期部5で決定するシンボル同期タイミングによって予め判っているから、そのシンボル同期タイミングに同期したサンプル点のみを選択してフィルタ部3でフィルタ処理することができる。故に、フィルタ部3のダウンサンプラ31におけるダウンサンプリング数を源信号のビットレートと同程度まで下げることができ、その結果、フィルタ部3の演算量を減少させることができてフルディジタル化による回路規模の増大を抑えることができる。

(もっと読む)

サンプルレート変換器

【課題】比較的小さいハードウェア量で、所望信号帯域において平坦な振幅特性と平坦な位相特性が得られ、かつ必要十分な折り返し信号除去能力を得る。

【解決手段】この発明は、周波数fsでサンプリングされた入力信号をフィードバックループによるフィルタリングによってサンプルレートを変換するサンプルレート変換器において、0からfs/N(Nは自然数)までの周波数帯域において少なくとも1より大きい利得で、入力信号とフィードバック信号を合成した合成信号を生成する生成手段(1)と、合成信号をN分の1のサンプルレートfs/Nにダウンサンプリングするダウンサンプラ(2)と、ダウンサンプリングされた合成信号をN倍のサンプルレートfsにアップサンプリングするアップサンプラ(3)と、アップサンプリングされた信号を、フィードバック信号として生成手段に出力する出力手段(3)とを具備して構成するようにしたものである。

(もっと読む)

71 - 80 / 199

[ Back to top ]