国際特許分類[H03H19/00]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 時間変化要素を用いる回路網,例.N一路フィルター (94)

国際特許分類[H03H19/00]に分類される特許

1 - 10 / 94

スイッチドキャパシタ積分器

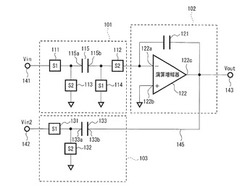

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

スイッチトキャパシタ積分器

【課題】スイッチトキャパシタ積分回路に用いられる第1のコンデンサと第2のコンデンサの電圧依存性の影響の低減及び小型化が可能な、新規な構造のスイッチトキャパシタ積分回路を提供すること。

【解決手段】第1のコンデンサ18と、前記第1のコンデンサ18の一端と入力端子16との間に接続される第1のスイッチ12と、前記第1のコンデンサ18の他端に出力端20が接続され、非反転入力端子28が定電位源に接続される差動増幅器24と、前記第1のコンデンサ18の一端と前記差動増幅器24の反転入力端子26との間に接続される第2のスイッチ14と、前記差動増幅器24の出力端20と反転入力端子26の間に接続される第2のコンデンサ22とを備えた。

(もっと読む)

スイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器

【課題】面積が小さく、消費電流を大幅に低減することができるスイッチトキャパシター積分回路、フィルター回路、物理量測定装置、及び電子機器等を提供する。

【解決手段】スイッチトキャパシター積分回路としての2重正相積分回路10は、第1の容量CAを有し、第1の期間において入力信号に対応した電荷を第1の容量CAに充電する第1の電圧電荷変換回路20と、第2の容量CBを有し、第2の期間において第1の容量CAに充電された電荷の一部を第2の容量CBに充電し、第2の容量CBに充電された電荷の一部を転送する第1の電荷積分回路30とを含む。

(もっと読む)

スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器

【課題】所望の信号伝達関数でより一層の出力雑音成分を低減できるスイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等を提供する。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

(もっと読む)

スイッチトキャパシタ回路

【課題】システムの性能劣化を避けつつ、システムの消費電力を低減する。

【解決手段】コンデンサC1と、コンデンサC1の入力側及び出力側にそれぞれ設けられたスイッチSW1〜SW4と、コンデンサC1の出力を受ける後段のオペアンプ204とを備え、スイッチSW1〜SW4の少なくとも一つの開閉状態に応じてオペアンプ204へ供給される電流値を切り替える。

(もっと読む)

離散時間アナログ回路及びそれを用いた受信機

【課題】フィルタの極の設定位置の自由度が高い、広帯域かつ急峻なフィルタ特性を有する離散時間アナログ回路および受信機を提供すること。

【解決手段】離散時間アナログ回路100は、ローテートキャパシタ回路150と、ローテートキャパシタ回路150の入力ライン又は出力ラインに接続され、入力電位又は入力電荷を増幅する増幅器141と、増幅器141に直列に配置され、互いに並列に配置される2個のヒストリキャパシタ143−1,143−2とを有する係数回路140と、2個のヒストリキャパシタ143−1,143−2のうち、増幅器141と接続されチャージされる第1のアクティブキャパシタと、増幅器141を介さずに入力ライン又は出力ラインと接続され、ローテートキャパシタ回路150と電荷共有される第2のアクティブキャパシタとのペアを順次変更するクロック生成回路110と、を具備する。

(もっと読む)

AD変換装置

【課題】アナログイコライザの前置を不要とするAD変換装置を提供する。

【解決手段】Nビット分解能を有するM個(M≧N+3)の逐次比較型AD変換回路と制御回路とを備え、各逐次比較型AD変換回路(i)は、入力アナログ信号のサンプリング電圧Vs(i)に相当する電荷Q(i)を保持する可変容量キャパシタCv1〜Cvm−1と、各可変容量キャパシタの容量の変更に応じて、逐次比較型AD変換回路(i)〜(i+m−2)内の、容量が変更された可変容量キャパシタCv1〜Cvm−1の端子間に現れる係数乗算電圧Vm(i)〜Vm(i+m−2)と、サンプリングタイミングT(i+m−1)に対応するサンプリング電圧Vs(i+m−1)とに基づいて、前補正電圧Vd(i+m−1)を生成する電圧補正回路と、Nビットのデジタル出力を生成する逐次比較部とを備え、可変容量キャパシタの容量を変化させる容量制御部を備える。

(もっと読む)

ダイレクトサンプリング回路

【課題】時分割統合された信号系列に対して、時分割で兼用する場合であっても、各系統間で信号の混ざりを回避するダイレクトサンプリング回路を提供する。

【解決手段】スイッチトキャパシタフィルタ160の前段に系統毎にヒストリキャパシタ153,155を接続し、スイッチトキャパシタフィルタ160の後段に系統毎にバッファキャパシタ173,175を接続し、スイッチトキャパシタフィルタ160のローテーションキャパシタと接続するヒストリキャパシタ及びバッファキャパシタを入力している時分割系統毎に切り替える。

(もっと読む)

信号モニタリングシステム

【課題】信号モニタリングシステムにおいて、応答速度およびモニタリング精度の両方を向上させる。

【解決手段】信号フィルタは、ノードと、第1端と、第2端と、前記ノード並びに前記第1および第2端に結合されたエネルギ蓄積回路とを有する。ノードは、入力信号および基準信号を選択的に受信する。第1端は、前記入力信号および基準信号によって特定された出力信号を提供する。第2端は、前記出力信号を示すフィードバック信号を受信する。エネルギ蓄積回路は、前記入力信号および基準信号に基づいて前記第1端で前記出力信号を発生させる。またエネルギ蓄積回路は、ノードを介して入力信号を受信するとともに、第2端を介してフィードバック信号を受信する、該動作を交互に実行する。信号フィルタの支配極は、第1入力信号およびフィードバック信号が交代されることについての周波数によって制御される。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

1 - 10 / 94

[ Back to top ]