国際特許分類[H03H7/18]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | インビーダンス回路網,例.共振回路;共振器 (15,336) | 回路網の部品として受動的電気素子のみを含む多端子対回路網 (1,834) | 移相回路網 (82)

国際特許分類[H03H7/18]の下位に属する分類

国際特許分類[H03H7/18]に分類される特許

1 - 10 / 29

干渉波抑制装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

制御回路および位相変調器

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

移相器およびその設計方法

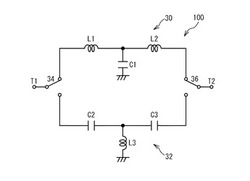

【課題】移相量のばらつきを抑制すること。

【解決手段】第1および第2インダクタと第1キャパシタとを備えるT型のLCLローパスフィルタと、第2および第3キャパシタと第3インダクタとを備えるT型のCLCハイパスフィルタと、を具備し、前記ローパスフィルタと前記ハイパスフィルタとの位相差により移相を行ない、移相を行なう高周波信号の特性インピーダンスをZ0、前記高周波信号の角周波数をω、移相量をΔΘとしたとき、各インダクタおよびキャパシタの値を製造ばらつきによるΔΘが小さくなるように設定する移相器。

(もっと読む)

直交信号生成回路、直交信号生成回路の調整方法、及び無線通信装置

【課題】高周波の広い範囲で周波数が高速で切り替わり、正確に位相が90度異なる直交信号を消費電力が少ない回路で生成する。

【解決手段】可変利得アンプ9によって増幅した信号を、ポリフェイズフィルタ1を通すことで、大まかに位相差が90度となる直交信号を生成する。ディジタル制御回路8からのディジタル信号で制御された可変利得アンプ2,3により、直交信号を増幅する。可変利得アンプ2,3の出力信号の振幅を振幅検出器4,5によって検出し、可変利得アンプ2,3の出力信号の振幅が等しくなるように、可変利得アンプの利得をディジタル制御回路8によって疎調整する。この疎調整に加えて、後述する微調整を行うことで、可変利得アンプ2,3の出力信号の振幅を等しくする。

(もっと読む)

90度移相器

【課題】IQ成分の位相誤差を調整することが可能な90度移相器を提供する。

【解決手段】フリップフロップ部とバイアス調整部BA1とが設けられている。フリップフロップ部は、互いに位相が180度だけ異なるクロック信号CKp_M、CKn_M、CKp_S、CKn_Sに従ってフリップフロップFF1の出力をフリップフロップFF2に入力し、フリップフロップFF2の出力をフリップフロップFF1に入力することで、クロック信号CKp_M、CKn_M、CKp_S、CKn_Sが2分周された互いに位相が90度ずつ異なる信号I、IX、Q、QXを生成する。バイアス調整部BA1は、フリップフロップ部のDCバイアスを調整することにより、フリップフロップFF1、FF2間でデータがやり取りされるタイミングを調整する。

(もっと読む)

逆相分配回路及びアンテナ装置

【課題】 良好な周波数特性を得つつ、小型でかつ広い周波数帯域にわたり動作する逆相分配回路を得る。

【解決手段】本発明における逆相分配回路は、所定の周波数帯域の中心周波数において、集中定数素子により構成されるT形またはΠ形の略90度の遅れ位相を持つ第1乃至第3の−90度回路と、略90度の進み位相を持つ第1の+90度回路と、前記第1の−90度回路と前記第1の+90度回路のそれぞれの一端と接続する入力端子と、前記第1の−90度回路の他端と接続する第1の出力端子と、前記第1の+90度回路の他端と接続する第2の出力端子と、を備え、前記第1の−90度回路と前記第1の+90度回路を同形とし、前記第2の−90度回路と前記第3の−90度回路を同形とし、かつ、それぞれの一端を接続し、前記第2の−90度回路の他端と前記第1の出力端子とを接続し、前記第3の−90度回路の他端と前記第2の出力端子とを接続する。

(もっと読む)

移相器

【課題】挿入損失の周波数特性のうち、通過位相差を与えられる周波数範囲における挿入損失が大きい。

【解決手段】一実施形態によれば、入力端子2および出力端子5の間に接続された一方の信号経路3と、一方の信号経路3に並列に設けられ入力端子2に一端が接続され出力端子5に他端が接続された他方の信号経路4と、一方の信号経路3および他方の信号経路4のいずれかに入力端子2からの高周波信号の経路を切換えるスイッチ回路16、17と、一方の信号経路3に設けられた第1ハイパスフィルタ8と、この第1ハイパスフィルタ8を主として一方の信号経路3に副次的に並列に付加された第1ローパスフィルタ9とを備え、この第1ローパスフィルタ9および第1ハイパスフィルタ8は、挿入損失特性のうち、高周波信号が一方の信号経路3によって通過位相差を与えられる周波数範囲における挿入損失を補償する移相器1が提供される。

(もっと読む)

左手/右手系複合伝送路

【課題】薄型を保ちつつ簡単にキャパシタ及びインダクタの値を制御することができる左手/右手系複合伝送路を提供する。

【解決手段】グランド板3に対して各々垂直に配置された互いに平行な一対の第1平行導体板41と、一対の第1平行導体板41間に挟まれかつ平行に配置された一対の第2平行導体板42と、一対の第2平行導体板42間に挟まれかつ平行に配置されると共にグランド板3側の一端がグランド板3に接続されるように配置された導体板43と、一対の第1平行導体板41と一対の第2平行導体板42との間をそれぞれ接続する一対の第1棒状導体44と、第2平行導体板42同士を接続する第2棒状導体45と、第2棒状導体45とグランド板3を接続する第3棒状導体46から構成される。一対の第3平行導体板5がグランド板3と離間して配置されると共に、導体ユニット4を挟みかつ第1平行導体板41に対して平行になるように配置される。

(もっと読む)

温度可変減衰器

【課題】2組設けられている90°位相遅延回路の削減ができ、小型化及びコストの低減を図るようにする。

【解決手段】主線路1Aと1Bの間に、第2サーミスタ(負温度係数温度可変抵抗体)3A、3Bをシリーズに設けると共に、この第2サーミスタ3Aと3Bの接続点と接地との間に第1サーミスタ2を接続する。そして、第2サーミスタ3Aと3Bの接続点と第1サーミスタ2との間に、静電容量Cの集中定数型コンデンサ5A,5Bと集中定数型インダクタ(コイル)6によりπ型に構成された集中定数型90°位相遅延回路を1組設けるようにする。この集中定数型90°位相遅延回路の代わりに、1/4波長分布定数伝送線路を設けてもよい。

(もっと読む)

90度ハイブリッド回路

【課題】異なる2つの周波数帯域で動作し、小形化が可能な90度ハイブリッド回路を得る。

【解決手段】略々正方形形状を構成するように第1〜第4の接続部5〜8を配置し、第1の接続部5に、第1の入出力端子1と、第1及び第4の直列共振回路9,12の一端と、第1の並列共振回路13の接地端でない一端とを接続し、第2の接続部6に、第2の入出力端子2と、第1の直列共振回路9の他端と、第2の直列共振回路10の一端と、第2の並列共振回路14の接地端でない一端とを接続し、第3の接続部7に、第3の入出力端子3と、第2の直列共振回路10の他端と、第3の直列共振回路11の一端と、第3の並列共振回路15の接地端でない一端とを接続し、第4の接続部8に、第4の入出力端子4と、第3及び第4の直列共振回路11,12の他端と、第4の並列共振回路16の接地端でない一端とを接続して構成する。

(もっと読む)

1 - 10 / 29

[ Back to top ]