国際特許分類[H03K17/30]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | スイッチ動作の前に所定のしきい値を設けるための変形 (99)

国際特許分類[H03K17/30]に分類される特許

1 - 10 / 99

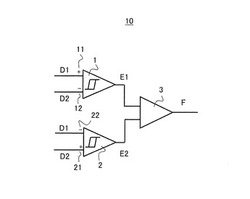

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

選択可能閾値リセット回路

【課題】低電圧試験のためのリセット回路及び方法を提供する。

【解決手段】低電圧試験回路125と、システム100および200と、集積回路パッケージ104および204における回路127の低電圧試験を実行する方法が、電源電圧の一部分である電圧を生成する電圧分割ラダー320、一部分を基準電圧と比較する比較器310、電圧分割ラダーのトポロジーを制御し、それによって一部分の値を変更するスイッチ350を含む、選択可能閾値リセット回路125を含み、スイッチは製品試験装置102および202からの信号によって制御され、信号は、選択可能閾値リセット回路のリセット閾値を標準リセット閾値未満に低減されるようにして、標準リセット閾値未満の電源電圧で回路を試験することを可能にする。

(もっと読む)

電圧識別装置及び時計制御装置

【課題】回路規模及び消費電流の増大を抑制しながら識別対象電圧の大きさを精度良く識別することができる電圧識別装置及び時計用制御装置を提供する。

【解決手段】基準電圧生成回路12と、被印加線18並びに電圧線VSH及び接地線GNDが導通可能となるように電圧線VSHと接地線GNDとの間に挿入されると共に、被印加線18に印加された識別対象電圧の大きさに応じてスイッチングを行うスイッチング回路20を備え、被印加線18に印加された識別対象電圧の大きさと閾値とを比較することにより識別対象電圧の大きさを識別する識別回路14と、識別回路14に対して識別対象電圧の大きさを識別させる間、電圧線VSHと接地線GNDとの間に流れる電流の大きさが所定の大きさに保たれるようにスイッチング回路20と接地線GNDとの間の抵抗22を制御可能とする制御部16と、を含む。

(もっと読む)

出力回路

【課題】回路規模が小さく、出力トランジスタのしきい値電圧がばらついてもノイズを抑えつつターンオフ時間を短縮する。

【解決手段】駆動信号SdがLの時、トランジスタT1がオン、T2がオフしてVGS(T3)がほぼ電源電圧Vccに等しくなりトランジスタT3がオンする。駆動信号SdがHになるとトランジスタT1がオフ、T2がオンする。トランジスタT4がオンするので抵抗R2がバイパスされ、トランジスタT3のゲート電荷はトランジスタT4、T2を通して急速に放電する。VGS(T3)がVth(T4)+VDS(T2)よりも低下すると、トランジスタT4はオフとなり、以後はトランジスタT3のゲート電荷が抵抗R2とトランジスタT2を通して緩やかに放電する。トランジスタT3、T4のしきい値電圧は一致する傾向があるので、VGS(T3)がVTH(T3)に低下した時点でトランジスタT4をオフできる。

(もっと読む)

半導体装置及び電子機器

【課題】トランジスタを用いたスイッチ回路を有するデジタル回路において、電源電圧、入力信号の振幅、トランジスタのしきい値電圧の関係に応じて適切に入力信号を補正し、好適な回路動作を可能とする。

【解決手段】電源電位(VDD、VSS)が供給される第1のトランジスタ(32、33)を有するスイッチ回路(31)と、入力信号が印加される入力端(IN)と第1のトランジスタの制御端子(ゲート)との間に接続された補正回路(34、36)とを有し、前記制御端子と入力端との間に接続された容量(C2、C3)と、該容量と前記制御端子との間のノード(N5、N6)と電源電位との間に設けられた、第1のトランジスタと概ね同じしきい値を有するダイオード接続された第2のトランジスタ(35、37)と、第2のトランジスタに直列に接続されたスイッチ(SW2、SW3)とを有するデジタル回路(30)を提供する。

(もっと読む)

ヒシテリシス装置

【課題】簡易な構成でヒシテリシス特性を付与する。

【解決手段】ヒシテリシス装置1000は、複数の閾値に対応するオフセット電圧を入力信号Vinに付加した調整信号Vxを出力する入力信号調整部300と、調整信号Vxに基づいて2値化した第1信号10aを出力するコンパレータ10と、入力信号調整部300を制御して複数の閾値ごとにオフセット電圧を切り替えるとともに、オフセット電圧の切り換えごとに第1信号10aを取得し、複数の閾値に対応する第1信号10aと前回の出力信号DETとに基づいて今回の出力信号DETを生成する判定部200とを備える。

(もっと読む)

半導体装置

【課題】電源電圧の変動に起因した書込電流の変動を抑制する。

【解決手段】ドライブ回路25において、第1のMOSトランジスタPMは、第1および第2の電源ノード28,29間にデータ書込線DLと直列に設けられる。第2のMOSトランジスタPSは、第1のMOSトランジスタPMと並列に設けられる。第3および第4のMOSトランジスタPa,Pbは、互いに同じ電流電圧特性を有する。第1の素子Eaは、第1および第2の電源ノード28,29間に第3のMOSトランジスタPaと直列に接続される。第2の素子Ebは、第1および第2の電源ノード28,29間に第4のMOSトランジスタPbと直列に接続され、第1の素子Eaの電流電圧特性曲線と交差する電流電圧特性を有する。比較器30は、第1の素子Eaにかかる電圧と第2の素子Ebにかかる電圧とを比較し、比較結果に応じて第2のMOSトランジスタPSをオンまたはオフにする。

(もっと読む)

モードコントロール回路

【課題】 パワーダウンモードを含む複数の動作モードを有する半導体集積回路において、モード切り換えを行うモードコントロール回路の消費電力を少なくする。

【解決手段】 制御電圧VCに基づきパワーダウンを設定するか解除するかの判定を行う回路としてオフセット付き電圧比較器30Aを設けた。制御電圧VCがオフセット電圧V0よりも低く、オフセット付き電圧比較器30Aがパワーダウン解除信号MD0を非アクティブレベルとしている間は、基準電圧発生回路10Aを動作させず、制御電圧VCとの比較に用いる基準電圧V1〜V3を出力させない。制御電圧VCがオフセット電圧V0を越えて上昇し、パワーダウン解除信号MD0がアクティブレベルになったとき、基準電圧発生回路10Aを動作させ、基準電圧V1〜V3と制御電圧VCとの比較によるモード切り換えを行わせる。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

1 - 10 / 99

[ Back to top ]