国際特許分類[H03K17/56]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電子的スイッチングまたはゲート,すなわち,メークおよびブレーク接点によらないもの (5,698) | 特定の構成要素の使用によって特徴づけられたもの (2,578) | 能動素子として半導体装置を用いるもの (2,114)

国際特許分類[H03K17/56]の下位に属する分類

二以上の形式の半導体装置の使用に特徴づけられた回路,例.BIMOS,IGBTのような複合装置 (31)

装置がトンネルダイオードであるもの

装置がバイポーラトランジスタであるもの (134)

装置が電界効果トランジスタであるもの (1,712)

装置が電極を2個だけもち,かつ負性抵抗を示すもの

バイポーラ半導体装置で3以上のPN接合を持つもの,例.サイリスタ,プログラムできるユニジャンクショントランジスタ,または4以上の電極をもつもの,例.シリコン制御スイッチ,または同一伝導領域に接続された2以上の電極をもつもの,例.ユニジャンクショントランジスタ (38)

国際特許分類[H03K17/56]に分類される特許

1 - 10 / 199

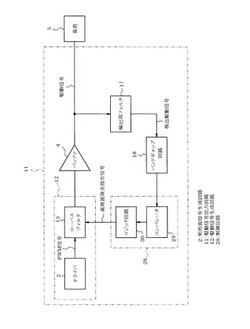

誘導性負荷の駆動回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

半導体集積回路

【課題】絶縁ゲート電界効果トランジスタ構造を有するトランジスタのスクリーニングを可能として、出力端子にサージ電圧が印加された場合のサージ電圧のエネルギー吸収能力を改善する。

【解決手段】集積回路ICは、トランジスタ2を含む出力バッファ回路100とプリドライバ300とを具備する出力回路10を内蔵する。出力バッファ回路100の出力OUTは、IC外部と接続可能である。プリドライバ300の出力はトランジスタ2の絶縁ゲート電界効果トランジスタ構造の制御ゲートに接続され、ソース領域と基板領域は第1接地線D_GNDに接続され、プリドライバ300は第2接地線L_GNDに接続される。第1と第2の接地線D_GND、L_GNDは第1と第2の接地端子PAD_G1、G2を介してIC外部と接続可能とされる。出力回路10は、第1と第2の接地線D_GND、L_GNDの間に接続された出力保護ダイオード11を更に具備する。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体装置

【課題】スイッチング素子のターンオン直後における、過電流保護回路の誤動作防止と過電流検出遅れ防止とを両立させる。

【解決手段】半導体装置は、スイッチング素子1のセンス端子に流れるセンス電流を電圧(センス電圧)に変換するセンス抵抗4と、センス電圧が閾値を越えたときにスイッチング素子1の保護動作を行う過電流保護回路3とを備える。過電流保護回路3は、上記閾値を、第1基準電圧VREF1またはそれよりも低い第2基準電圧VREF2に切り替えることができる。過電流保護回路3は、スイッチング素子1が定常状態のときは、上記閾値を第2基準電圧VREF2とし、スイッチング素子1のターンオン直後のミラー期間のときは、上記閾値を第1基準電圧VREF1に設定する。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

半導体スイッチの制御装置

【課題】半導体スイッチ素子に並列に接続される保護回路の異常を検出できる半導体スイッチ素子の制御回路を得る。

【解決手段】半導体スイッチに印加される電圧を抑制するために半導体スイッチに並列に接続された保護回路と、駆動回路の出力ゲート電圧が予め設定された電圧以上あることを検出し、半導体スイッチのオン・オフ状態を判別するゲート電圧検出手段と、半導体スイッチの主端子電圧を検出する主電圧検出手段と、駆動回路に与えられた駆動信号により、駆動指令がオン指令の場合はゲート電圧状態を選択し、駆動指令がオフ指令の場合は主電圧状態を選択する選択手段と、選択手段の出力を絶縁して低圧回路に伝達する第一の信号絶縁手段と、選択手段が選択して出力したゲート電圧状態・主電圧状態と半導体スイッチの駆動指令とを比較し、半導体スイッチの正常又は異常を判別する判別手段とを備える。

(もっと読む)

1 - 10 / 199

[ Back to top ]