国際特許分類[H03K19/00]の内容

国際特許分類[H03K19/00]の下位に属する分類

信頼性を増すための変形 (215)

フェイルセーフ回路 (8)

スイッチ動作の高速化のための変形 (58)

結合装置;インターフェイス装置 (1,927)

特定の構成要素を用いるもの (1,730)

論理機能によって特徴づけられたもの,例.アンド,オア,ノア,ノット回路 (214)

国際特許分類[H03K19/00]に分類される特許

1 - 10 / 669

半導体集積回路、半導体集積回路の制御方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体集積回路の製造方法

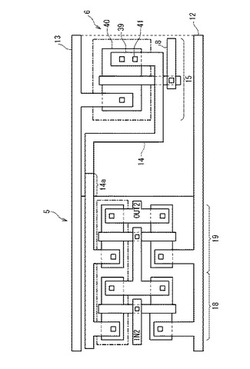

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

クロックゲーティング回路およびバスシステム

【課題】トランザクションを単位として扱うバスシステムにおいて消費電力を低減する。

【解決手段】クロックゲーティング回路は、クロックイネーブル信号生成部とマスククロック生成部とを備える。クロックイネーブル信号生成部は、バスシステムを複数のリージョンに分割した各々においてアウトスタンディングトランザクションの数を計数することにより複数のリージョンの各々のためのクロックイネーブル信号を生成する。マスククロック生成部は、複数のリージョンの各々のためのクロックイネーブル信号によってクロックをマスクしてマスククロックを生成する。

(もっと読む)

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

スイッチ回路

【課題】多くの個別素子による回路を用いることなく、容易に簡素な回路構成で端子外れ検出を行うことが可能なスイッチ回路の提供。

【解決手段】ゲートがセンサ回路に接続され、ドレインが第1の電圧制限抵抗に接続された第1の出力ドライバと、物理量検出信号出力端子と接地端子の間に接続された第2の電圧制限抵抗と、非反転入力端子が第1の基準電圧回路に接続され、反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第1の比較器と、反転入力端子が第2の基準電圧回路に接続され、非反転入力端子が前記物理量検出信号出力端子に接続され、出力が論理回路に接続された第2の比較器と、ゲートが前記論理回路の出力に接続され、ドレインが断線診断信号出力端子に接続された第2の出力ドライバで構成した。

(もっと読む)

論理回路、半導体集積回路

【課題】供給される電源電圧の変動を抑制することができる論理回路及び当該論理回路が搭載される半導体集積回路を提供すること。

【解決手段】本発明の一態様であるバッファ回路100は、バッファ部11、電圧検出部12及びスイッチ部13を有する。バッファ部11は、電源端子Ts1又は電圧レギュレータ1と電源端子Ts2との間に接続されることにより電源供給され、入力信号INと同論理の信号を出力端子Toutへ出力する。電圧検出部12は、出力端子Toutの電圧を検出し、検出結果に基づく検出信号Sdetを出力する。スイッチ部13は、検出信号Sdetに応じて、バッファ部11を電源端子Ts1又は電圧レギュレータ1と接続する。

(もっと読む)

半導体装置及びその動作電源電圧制御方法

【課題】半導体装置及びその動作電源電圧制御方法を提供する。

【解決手段】動作電圧を可変とする複数の処理ユニットと、これら処理ユニットを制御するコントローラを有するLSIと、LSIからの処理ユニット毎に対応した電源供給の要求に応じて電源電圧を処理ユニットに供給する電源制御ユニットと、処理ユニット毎に電源制御ユニットに指示する電源電圧指示値を保持する書き換え可能な不揮発メモリと、を備え、コントローラは、処理ユニット毎に不揮発メモリに保持された電源電圧指示値を取得し、取得した電源電圧指示値を電源制御ユニットに転送する半導体装置。

(もっと読む)

1 - 10 / 669

[ Back to top ]