国際特許分類[H03K19/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065)

国際特許分類[H03K19/08]の下位に属する分類

バイポーラトランジスタを用いるもの (24)

電界効果トランジスタを用いるもの (1,019)

サイリスタを用いるもの

トンネルダイオードを用いるもの (1)

国際特許分類[H03K19/08]に分類される特許

1 - 10 / 21

レベルシフト回路

【課題】占有面積が小さく、温度変化や素子のバラツキの影響を受け難く、さらに、ノイズを低減することで高品位のレベルシフトを実現することができるレベルシフト回路を提供する。

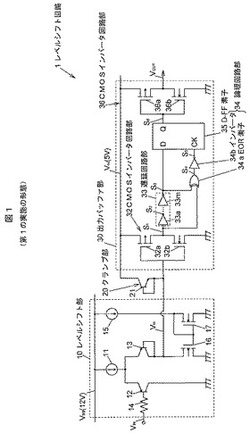

【解決手段】レベルシフト回路1は、主に、第1の信号(VIN)をレベルシフトして第2の信号(Vm)を出力するレベルシフト部10と、pMOSトランジスタ32aとnMOSトランジスタ32bを含み、第2の信号を反転させた第3の信号(S1)を出力するCMOSインバータ回路部32、偶数個のインバータ素子(第1のインバータ33a〜第mのインバータ33m)を含み、第3の信号を遅延させた第4の信号(S3)を生成する遅延回路部33、論理素子を含み、第3の信号及び第4の信号が入力して第5の信号(S5)を出力する論理回路部34、及び第4の信号と第5の信号が入力するD−FF素子35、を含む出力バッファ部30と、を備える。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

半導体装置

【課題】半導体素子の劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置40は、正極41及び負極42と、正極41と負極42の間に配置される出力電極43と、正極41と出力電極43を接続する正側スイッチング素子51と、正極41と出力電極43を接続し、正側スイッチング素子51とは電流を逆方向に流す正側ダイオード52と、負極42と出力電極43を接続する負側スイッチング素子61と、負極42と出力電極43を接続し、負側スイッチング素子61とは電流を逆方向に流す負側ダイオード62と、を備える。正極41及び負極42の電極厚さは、出力電極43の電極厚さよりも薄く設定される。

(もっと読む)

レベルシフト回路

【課題】バッテリの電源投入時等の電源電圧の急激なオーバーシュートに対する耐性を向上させるレベルシフト回路を提供する。

【解決手段】レベルシフト回路1は、バッテリからの高電圧レベルの入力信号VINを入力するレベルシフト部10と、レベルシフト部10の中間信号Vmを一定以下に制限するクランプ部20と、中間信号をより低電圧のCMOSレベルで出力する出力バッファ部30とを備える。出力バッファ部30の初段においてpMOSトランジスタ31の負荷を抵抗32とすることにより、電源電圧のオーバーシュートに対する耐性を向上させる。

(もっと読む)

ドライバ回路および試験装置

【課題】汎用性の高いデバイスを実現する。

【解決手段】与えられた入力信号に応じた出力信号を出力端から出力するドライバ回路であって、定電圧源と出力端との間に設けられる出力抵抗部と、入力信号に応じて出力端の電圧をスイッチングする出力スイッチ部と、出力抵抗部の抵抗値を切り替える切替部と、を備え、出力抵抗部は、定電圧源と出力端との間にソース−ドレインが接続された出力抵抗用FETを有し、切替部は、出力抵抗用FETのゲート端子に制御電圧を与えて、出力抵抗用FETのソース−ドレイン間を指定された抵抗値に切り替えるドライバ回路を提供する。

(もっと読む)

電流制限回路

【課題】回路面積を削減しつつ、より適切に電流を制限することが可能な電流制限回路を提供する。

【解決手段】電流制限回路は、第1の端子と、第1の端子との間に負荷回路を接続した場合に、第1の端子よりも電位が低くなる第2の端子と、第1の端子と第2の端子との間に接続され、n型MOSトランジスタである第1のトランジスタと、第1のトランジスタのソースと第2の端子との間に接続され、MOSトランジスタである第2のトランジスタと、第2のトランジスタのソース・ドレイン間の電圧を検知し、検知された検知電圧に基づいて、第1のトランジスタのゲートに印加する第1の電圧を制御する第1の制御回路と、第2のトランジスタのゲートに印加する第2の電圧を制御する第2の制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

デジタル信号を増幅させるための回路構成、及びバスシステムのためのトランシーバ回路

本発明は、出力回路の入力接続口(78)に印加されたデジタル入力信号(IN)を増幅させるための、バスシステム(11)のためのトランジスタ回路(21)のための出力回路(61)であって、出力回路(61)は、相補回路内にトランジスタ段(63)を有し、当該相補回路は、2つの互いに相補的に構成され直列に接続されたブランチ(65、75)を含み、各ブランチ(65、75)は、電界効果トランジスタ(M1、M2)を有する、上記出力回路(61)に関する。出力信号の立ち上がりエッジの時間(t1)と、出力信号(OUT)の立ち下がりエッジの時間(t2)と、が可能な限り僅かに異なる出力回路(61)を示すために、各ブランチ(65、75)がそれぞれ、当該ブランチ(65、75)の電界効果トランジスタ(M1、M2)のドレインソース区間によって直列に接続された電源(71、77)を有し、各電源(71、77)は、同ブランチ(65、75)の電界効果トランジスタ(M1、M2)のドレインソース区間が少なくとも部分的に伝導性である場合に、当該ブランチ(65、75)を通って流れる電流を生成するために構成され、1のブランチ(65、75)の電源(71、77)によって生成可能な電流(I1、I2)は、他のブランチ(75、65)の電源(77、71)によって生成可能な電流に、少なくとも実質的に対応することが提案される。 (もっと読む)

TMDS符号化信号を伝送する回路装置及び方法

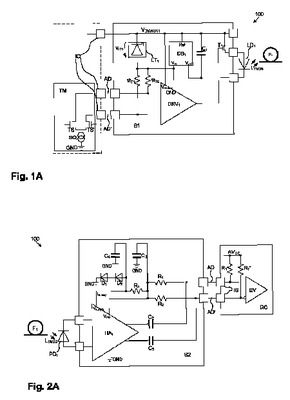

少なくとも部分的に、特に少なくともタイムスロット方式でTMDS符号化され、且つ特に少なくとも1つのDVIデータ接続、及び/又は、少なくとも1つのHDMIデータ接続に割り当てられた信号を、少なくとも1つのデータソースから少なくとも1つのデータシンクへ安価に伝送する回路装置(100;100’)及び方法を提供するために、

駆動回路(S1;S1’)は、上流に接続され且つ前記データソースに割り当てられた少なくとも1つの接続インターフェース(IQ)によって、約5ボルトの供給電圧を含み、特に約55ミリアンペア以下でチャージすることができる、供給電圧(VDVI/HDMI)を供給されること、

前記駆動回路(S1;S1’)の下流に接続された少なくとも1つの発光素子(LD1)、特に少なくとも1つの光ダイオード、少なくとも1つの発光ダイオード、少なくとも1つのレーザダイオード、あるいは少なくとも1つの半導体レーザを含む少なくとも1つのレーザによって、電気的なTMDS符号化信号を電気−光変換して、前記TMDS符号化信号を与えられた光(LTMDS)として、少なくとも1つの光ファイバー(F1)、特に少なくとも1つのガラス繊維又は少なくとも1つのプラスチックファイバーを含む少なくとも1つのプラスチック材料繊維に、連結すること、

少なくとも1つのTMDSトランスミッタ(TM)からデータソースに割り当てられた前記接続インターフェース(IQ)へ供給される直流電流部分は、前記駆動回路(S1;S1’)によって前記発光素子(LD1)を制御する変調信号電流に変換されること、

前記TMDS符号化信号を与えられた前記光(LTMDS)は、少なくとも1つの光吸収素子(PD1)、特に少なくとも1つのフォトダイオードによって、前記光ファイバー(F1)から取り出されて、光−電気変換され、前記光吸収素子(PD1)の下流且つ前記データシンクに割り当てられた少なくとも1つの接続インターフェース(IS)の上流に接続された少なくとも1つのトランスインピーダンス変換回路(S2;S2’)に供給され、前記トランスインピーダンス変換回路(S2;S2’)は、少なくとも1つの差動ペア配線(AD、AD’)によって印加される直流電圧部分によって提供されることが提案される。  (もっと読む)

(もっと読む)

1 - 10 / 21

[ Back to top ]