国際特許分類[H03K19/0948]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 半導体装置を用いるもの (1,065) | 電界効果トランジスタを用いるもの (1,019) | MOSFETを用いるもの (616) | CMOSを用いるもの (413)

国際特許分類[H03K19/0948]に分類される特許

1 - 10 / 413

信号送信回路

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

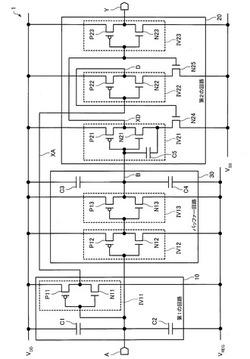

レベルシフター回路、集積回路装置、電子時計

【課題】 出力信号にスパイクノイズが乗ることや、応答速度が遅くなることを防止するレベルシフター回路を提供する。

【解決手段】 第1の高電位と第1の低電位とを電源電位とする第1の電位系の入力信号Aを受け取り、第1の電位系の信号である第1の信号XAを出力する第1の回路10と、第2の高電位と第2の低電位とを電源電位とする第2の電位系の、入力信号に応じた出力信号Yを生成する第2の回路20と、入力信号を受け取り、第1の電位系の信号であって入力信号と論理的に等価な第2の信号Bを生成するバッファー回路と、を含み、第2の回路は、第2の信号を受け取り、第3の信号XDを出力する初段インバーターと、第1の信号に基づいて、初段インバーターと第2の高電位を供給する電源又は第2の低電位を供給する電源との接続、切断を切り換える初段スイッチと、を含み、第3の信号に基づいて出力信号を生成する。

(もっと読む)

半導体装置

【課題】低電圧動作を実現可能なレベルシフト回路を提供する。

【解決手段】入力電位は、GNDとVDDとの間で切り替わる。電源端子には、VDDよりも高いVDDOが印加される。レベルシフト回路は、クランプ回路と接続制御回路を備える。クランプ回路は、ソースが第1ノードに接続され、ドレインがP側出力端子に接続され、ゲートが電源端子に接続された第1NMOSトランジスタと、ソースが第1ノードに接続され、ドレインがN側出力端子に接続され、ゲートがグランド端子に接続された第1PMOSトランジスタと、を備える。入力電位がGNDとVDDの一方の場合、接続制御回路は、P側出力端子にVDDOを印加し、且つ、N側出力端子とグランド端子との間の電気的接続を遮断する。入力電位がGNDとVDDの他方の場合、接続制御回路は、N側出力端子にGNDを印加し、且つ、P側出力端子と電源端子との間の電気的接続を遮断する。

(もっと読む)

半導体装置

【課題】容量を充放電させ信号を遅延させる回路の遅延時間の温度依存性を緩和し回路規模の増大を抑制可能とした半導体装置の提供。

【解決手段】互いに異なる電源電圧を与える第1の電源(VDD)と第2の電源(VSS)の間に直列に接続され、制御電極が共通に接続された第1及び第2のFET(M11、M12)と、前記第1及び第2のFETの間に接続する第1の回路を有するインバータを備え、前記第1の回路は、互いに並列に接続された第1の抵抗素子(R12)と第3のFET(M13)を備え、前記第1の抵抗素子(R12)の抵抗値は正の温度特性を有し、前記第3のFET(M13)は、その動作範囲に、第3のFET(M13)の端子間抵抗が、第1の抵抗素子(R12)の温度特性と逆極性の負の温度特性を示す領域を含む。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

入力回路

【課題】高電位信号を低電位信号に変換する入力回路であって、適切なターゲット反転電位で動作可能な入力回路を提供する。

【解決手段】入力回路は、インバータ、第1パス制御回路、及び第2パス制御回路を備える。インバータの入力は第1ノードに接続される。ターゲット反転電位は、インバータの反転電位よりも高い。第1パス制御回路は、入力電位がターゲット反転電位より低い場合、入力端子と第1ノードとの間の電気的接続を遮断し、入力電位がターゲット反転電位より高い場合、入力端子と第1ノードとを電気的に接続する。第2パス制御回路は、入力電位がターゲット反転電位より低い第2反転電位より低い場合、グランド端子と第1ノードとを電気的に接続し、入力電位が第2反転電位より高い場合、グランド端子と第1ノードとの間の電気的接続を遮断する。

(もっと読む)

半導体回路

【課題】耐放射線特性の優れた半導体回路を提供することを目的とする。

【解決手段】複数のpMOSトランジスタ11,12を直列に接続した第1の回路ブロック1と、複数のnMOSトランジスタ21,22を直列に接続した第2の回路ブロック2とを備え、少なくとも1つの前記pMOSトランジスタ12のゲート及び/又は少なくとも1つの前記nMOSトランジスタ21のゲートを入力端子Vinに接続し、少なくとも1つの他のpMOSトランジスタ11のゲート及び/又は少なくとも1つの他のnMOSトランジスタ22のゲートに、オン電圧を印加する半導体回路。

(もっと読む)

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

半導体装置

【課題】相補の信号によりプルアップバッファ回路とプルダウンバッファ回路を制御し、レベルシフタ関連回路をコンパクトに構成する。

【解決手段】半導体装置10は、プルアップバッファ回路100とプルダウンバッファ回路200を排他的にオン・オフ制御することによりデータ端子DQからデータを出力する。シリアライザ300は、相補な内部データ信号DT1/DC1を出力する。レベルシフタ370は、内部データ信号DT1/DC1の電圧レベルを変換し、相補な内部データ信号DT2/DC2を同時生成する。プルアップバッファ回路100とプルダウンバッファ回路200は、この変換後の内部データ信号DT2/DC2により制御される。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

1 - 10 / 413

[ Back to top ]