国際特許分類[H03K19/173]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 論理回路,すなわち,1出力に作用する少なくとも2入力を持つもの;反転回路 (4,821) | 特定の構成要素を用いるもの (1,730) | 構成要素として基本的論理回路を用いるもの (575)

国際特許分類[H03K19/173]の下位に属する分類

マトリクス形状で配列されたもの (186)

国際特許分類[H03K19/173]に分類される特許

1 - 10 / 389

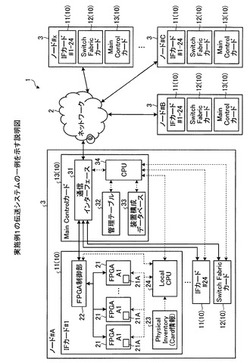

プラグインカード収容装置及びプラグインカード制御方法

【課題】コンフィグデータ提供に要する処理負荷及び通信帯域の集中を分散できる。

【解決手段】FPGA21を搭載したプラグインカード10と、管理テーブル32を参照して、ネットワーク2に接続された異なるノード3に対してFPGA21のコンフィグデータのダウンロードを要求する主制御カード13内のCPU34とを有する。CPU34は、ダウンロード要求に応じてダウンロード元のノード3から取得されたコンフィグデータを、FPGA制御部22を通じて、FPGA21内のメモリ21Aに格納する。更に、CPU34は、FPGA21内のメモリ21A内のコンフィグデータに基づき、当該FPGA21に対するコンフィグレーションを実行する。

(もっと読む)

信号処理ユニット及びこれを備える統合管理システム

【課題】コンフィギュレーションデータの更新情報を極めて簡素な信号で表現させ得る信号処理ユニットを提供する。

【解決手段】信号処理ユニット100は、コンフィギュレーションデータの更新情報が周波数信号によって表現され、当該周波数信号がFPGAから出力される。また、CPUでは、入力された周波数信号の周波数fに基づいて、コンフィギュレーションデータの更新情報を認識する処理を行うこととされる。このため、FPGAでは、一つのデータpinから更新情報に係る信号を出力させることが可能となり、当該FPGAに配備される他のデータpinを有効に利用できる。また、CPUでは、周波数信号の周波数fに基づいて更新情報を特定できるので、パルスエッジ等の間隔を検出することで直ちに更新情報を認識することが可能となる。

(もっと読む)

FPGA内部回路変更方法および画像形成装置

【課題】FPGA内部回路を動的に書き換えた後の制御に待ち時間を発生させないFPGA内部回路変更方法および画像形成装置を提供する。

【解決手段】画像形成装置は、複数のコネクタから受信された信号を検知する検知手段と、検知手段による信号の検知をASICに通知する信号検知通知手段と、信号検知通知手段による信号検知通知を受けたASICにより複数のメモリの何れかから読み出された内部回路の書換情報に基づいて一の内部回路が動作中に他の内部回路を書き換える書換手段と、他の内部回路の書換完了をASICに通知する書換完了通知手段と、書換完了通知手段による書換完了通知と同時に出力切替回路及び出力変更回路を切り替える回路切替手段を備える。

(もっと読む)

情報処理装置及び演算処理方法

【課題】アクセラレータで演算処理される機能に応じてプログラマブルデバイスの構成を適正化することにより、アクセラレータによる演算処理の効率化と省エネを図る。

をする。

【解決手段】コンフィギュレーションデータにより構成又は再構成可能なプログラマブルデバイス220を有するアクセラレータ200を使用して演算処理を実行する情報処理装置であって、コンフィギュレーションデータが機能別に複数格納された領域内から前記演算処理の機能に応じたコンフィギュレーションデータに関する情報を選択するデータ選択部120と、前記選択されたコンフィギュレーションデータに関する情報を前記アクセラレータ200に転送するデータ転送部125と、を備える情報処理装置が提供される。

(もっと読む)

記録装置及びその電源投入時の動作方法

【課題】命令コードを格納したフラッシュメモリ等の制御信号をFPGA等により生成する論理を実現する場合、FPGAのコンフィギュレーションに失敗すると情報処理装置が起動できないという課題があった。

【解決手段】FPGAがコンフィギュレーションに失敗した場合は、その成否を通知する信号を入力とする選択信号制御回路がパラレルEEPROMの選択信号を生成する。これに応じて、プロセッサは、例えば、パラレルEEPROMに格納されたコンフィギュレーションの失敗をユーザに通知するための命令コードを実行する。

(もっと読む)

情報処理回路

【課題】

出力電圧が可変な電源を適用していない場合や電源を複数部品で共有している場合においても、PLDの消費電力を低減することが出来る情報処理回路を提供する。

【解決手段】

再構成可能な論理回路と、回路データを格納する記憶素子とから成る情報処理回路であって、記憶素子に格納された前記回路データは、前記再構成可能な論理回路の製造プロセスを検出するプロセス検出回路データと、前記検出された製造プロセスに応じたタイミング対策を施した複数の再構成用回路データであること特徴とする情報処理回路。

(もっと読む)

FPGAのコンフィギュレーション制御回路、FPGA装置及び方法、並びに、コンフィギュレーションデータ更新方法

【課題】メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGAのコンフィギュレーションを高い信頼性をもって確実に行えるコンフィギュレーション制御回路、FPGA装置及び方法を提供する。

【解決手段】FROM12には、同じ内容のコンフィギュレーションデータが複数個格納されている。信号制御部08が、FPGA01にコンフィギュレーションのトリガを与えると、FPGA01は、FPGA01がデータの読み出し先として指定するFROM12の指定領域に格納されているデータを読み出して、コンフィギュレーションを行う。コンフィギュレーションが失敗した場合には、信号制御部08は、FROM12の指定領域を切り替え、FPGA01がFROM12の切り替え後の指定領域から別のデータを読み出してコンフィギュレーションするためのトリガをFPGA01に与える。

(もっと読む)

不揮発性プログラマブルロジックスイッチ

【課題】メモリの選択的な書き込みを行う際のパストランジスタのゲート絶縁膜の破壊を防ぐとともにパストランジスタのゲート絶縁膜を薄くすることを可能にし、かつメモリの微細化によって書き込み効率が損なわれない不揮発性プログラマブルロジックスイッチを提供する。

【解決手段】第1端子と、第2端子と、メモリ状態を制御する制御信号を受ける第3端子とを有する第1メモリと、ソース/ドレインの一方が第2端子に接続される第1トランジスタと、第1トランジスタのソース/ドレインの他方にゲートが接続される第2トランジスタとを備えた、第1セルおよび第2セルを有する。第1セルの第1メモリの第3端子と、第2セルの第1メモリの第3端子は共通に接続され、第1セルに書き込みを行う場合、第3端子が書き込み電源に接続され、第1セルの第1端子は接地電源に接続され、第2メモリの第1端子は書き込み防止電源に接続される。

(もっと読む)

情報処理装置、演算方法およびプログラム

【課題】 再構成可能なプログラマブル・デバイスを搭載するアクセラレータと連携して処理を実行する情報処理装置、演算方法およびプログラムを提供すること。

【解決手段】

本発明の情報処理装置110は、プログラマブル・デバイス150に接続されている。情報処理装置110は、各々前記プログラマブル・デバイス上で実現させる機能を定義する構成データが、複数格納される構成データ蓄積手段120と、各々対応する構成データによりプログラマブル・デバイス150上に実現される機能を利用するソフトウェア・プログラムが、複数格納されるプログラム蓄積手段118と、プログラマブル・デバイス150に、複数の構成データのうち選択された選択機能に対応する構成データを転送し、構成を要求する構成要求手段112とを含む。

(もっと読む)

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

1 - 10 / 389

[ Back to top ]