国際特許分類[H03K21/08]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | パルス計数器または周波数分割器の細部 (119) | 出力回路 (10)

国際特許分類[H03K21/08]の下位に属する分類

論理回路を包含するもの (4)

並列読出し回路をもつもの (3)

蓄積された数の直列読出し回路をもつもの (1)

国際特許分類[H03K21/08]に分類される特許

1 - 2 / 2

クーロンカウンタ、そのダイナミックレンジ可変方法

【課題】回路規模を縮小し、測定電流のダイナミックレンジ及び電流分解能を可変にして最適化を図り、誤差の少ないカウント値を出力可能なクーロンカウンタを提供する。

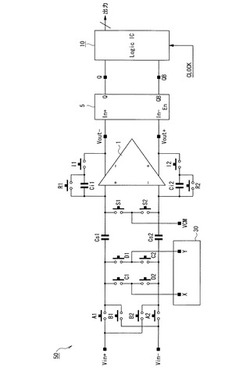

【解決手段】センス抵抗両端に生じる電位差の入力電圧に比例したカウント値を出力するクーロンカウンタであって、そのIC部50は、基準電圧発生回路30からの電圧値可変で設定された基準電圧の印加、スイッチ素子の操作により、入力電圧をサンプリング容量Cs1、Cs2でサンプリングし、それに比例する電圧を積分容量Ci1、Ci2で積分する積分回路と、積分回路からの出力電圧Vout−をVCMと比較して、Vout−がVCM以上では信号Q、VCMよりも低い場合は信号QBを出力するコンパレータ5と、信号Q、QBとを一定時間カウントしてカウント値を出力する内部カウンタ、カウント値に含まれるオフセット値を保持するレジスタを含むロジック回路10と、を備える。

(もっと読む)

グレイコードカウンタおよび表示装置

【課題】遅延フリップフロップの個数を少なくして、消費電流を低減したグレイコードカウンタを提供する。

【解決手段】グレイコードカウンタは、グレイコードの各ビットQ3,Q2,Q1,Q0を保持する4つのDFF11,12,13,14、参照ビットQbを作成するための参照ビット作成回路30、(Qb,Q0,Q1)をデコードするデコード回路を備えている。4つのDFF11,12,13,14はリセット信号RESETでリセットされ、基準クロックCLKに同期してデータを保持し、かつ遅延する。つまり、DFF11,12,13,14は、基準クロックCLKの立ち上がりに同期して、データ入力端子Dからあるデータを取り込んで保持し、次の基準クロックCLKの立ち上がりに同期してそのデータをデータ出力端子Qから出力する。

(もっと読む)

1 - 2 / 2

[ Back to top ]