国際特許分類[H03K23/00]の内容

国際特許分類[H03K23/00]の下位に属する分類

ゲート信号またはクロック信号がすべての段に印加されるもの,すなわち.同期形計数器 (94)

ゲートまたはクロック信号がすべての段には印加されないもの,すなわち,非同期形計数器 (4)

底または基数が2のべきないもの (126)

継電器を用いるもの

磁気コアまたは強誘電容量を用いるもの

オプトエレクトロニクス装置を用いるもの

2電極のみをもつ半導体装置,例.トンネルダイオード,多層ダイオード,を用いるもの

ガス入り管を用いるもの

サイリスタまたはユニジャンクショントランジスタを用いるもの

可逆的なもの

国際特許分類[H03K23/00]に分類される特許

1 - 10 / 67

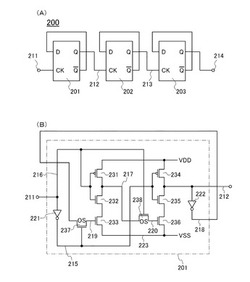

分周回路、及び分周回路を用いた半導体装置

【課題】消費電力を抑え、占有面積が小さい半導体装置を提供する。

【解決手段】フリップフロップ回路を構成するトランジスタに、チャネルが酸化物半導体に形成されるトランジスタを用いることで、トランジスタ数を低減し、消費電力が少なく、占有面積が小さい分周回路を実現する。また、該分周回路を用いることで、動作が安定し、信頼性の高い半導体装置を実現することができる。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

カウンター回路

【課題】回路規模及び/又は消費電力を従来よりも低減しながら、倍精度の計測を行うカウンター回路を実現する。

【解決手段】このカウンター回路は、計測期間において、クロック信号の立ち上がりエッジに同期してパルス数をカウントすることにより、第1カウント値を生成する第1の回路と、計測期間において、クロック信号の立ち下がりエッジに同期してパルス数をカウントすることにより、第2カウント値を生成する第2の回路と、計測期間におけるクロック信号の立ち上がりエッジと立ち下がりエッジとの前後関係を表すフラグ情報を保持する第3の回路と、フラグ情報に従って第1カウント値及び第2カウント値をデコードすることにより、クロック信号の周期に対して倍精度の計測カウント値を出力する第4の回路とを含む。

(もっと読む)

CMOSインバータ型高周波分周器

【課題】無線通信機器等に用いられるCMOSインバータ型高周波分周器を低消費電流にて実現する。

【解決手段】各々インバータ及び1つ以上のスイッチから構成された第1〜第4のラッチ機能付インバータ4,5,6,7と、第1及び第2のトランス8,9とで分周器を構成する。従来用いていた“2つのインバータを正帰還にして構成されたラッチ”は、不要となり、その代役としてトランス8,9を用いる。

(もっと読む)

累積加算回路

【課題】累積加算回路の消費電力を削減すること。

【解決手段】累積加算回路は、加算回路と、カウンタと、クロックゲーティング制御回路とを備える。加算回路は、所定ビットのデータを累積加算し、桁上げが発生した場合に桁上げ信号を活性化する。カウンタは、桁上げ信号が活性化されているときにカウントアップを行い、Nビットのカウント値を累積加算結果の上位桁として出力する。カウンタは、カウント値のそれぞれのビットをラッチするNビットレジスタを備える。桁上げ信号の活性化に応じて値が変化するビットを保持するレジスタは、活性レジスタである。クロックゲーティング制御回路は、加算回路から桁上げ信号を受け取り、且つ、カウンタからカウント値を受け取る。桁上げ信号が活性化された場合、クロックゲーティング制御回路は、カウンタから受け取ったカウント値を参照することによって、活性レジスタへのクロック供給だけを活性化し、それ以外のクロック供給を非活性化する。

(もっと読む)

分周装置および制御回路

【課題】本発明は、周期が変化する入力パルス列を分周し、分周したパルス列のジッタをできるだけ抑制することにある。

【解決手段】分周装置1は、第1変数および第2変数が互いに異なる正の整数をとり、第1変数に対する第2変数の比で表わされる分周比で入力パルスを分周可能な分周装置であって、入力パルスの周期にわたって、一定の周波数を持つ基準クロックをカウントするカウンタ回路(12)と、カウンタ回路によって得られた第1カウント値を第1変数が示す値に分割する演算を行うと共に、基準クロックのカウントを開始し、当該カウントによる第2カウント値が第1カウント値を分割した値に達する度に、一のパルスを出力する演算出力回路(13、14)と、演算出力回路の出力パルス列を第2変数が示す値で分周したパルスを出力する分周回路(15)と、を有する。

(もっと読む)

カウンタ回路、アナログデジタルコンバータ、カウンタ回路とアナログデジタルコンバータを備えた装置及びカウンティング方法とアナログデジタル変換方法

【課題】カウンタ回路、これを含む装置及びカウンティング方法を提供すること。

【解決手段】

カウンタ回路はバッファ部及びリップルカウンタを含む。バッファ部はカウンティング動作の終了時点から少なくとも1つの入力クロック信号をラッチして少なくとも1つの下位ビット信号を発生する。リッブルカウンタは下位ビット信号のうち1つに相応するラッチ出力信号に応答して順次にトグリング(toggling)する上位ビット信号を発生する。カウンタ回路は入力クロック信号のサイクル周期ごとに2回以上のカウンティングを遂行して向上した動作速度及び動作マージンを有し、ビット信号のトグリング回数を減らし消費電力を低減する。

(もっと読む)

カウンタ回路、及びその方法

【課題】デジタル論理回路で扱い易く、回路の実装面積を小さくすることができるカウンタ回路、及びその方法を提供する。

【解決手段】カウンタ回路であって、複数のフリップフロップ回路と、自身に入力される入力信号、ロー信号、及びハイ信号のうち、何れか1つを選択して出力する複数のスイッチ回路とを交互に接続する。第1のパルス列と第2のパルス列のパルス数をカウントする期間の場合は、前記入力信号を出力するようにスイッチ回路を制御する。第1のパルスから第2のパルスに切り替わる場合は、ロー信号を出力してからハイ信号を出力するようにスイッチ回路を制御することで、現在のカウント値を1の補数に変換させる。第2のパルス列をカウントする期間に入ると、1パルスをカウンタ回路に入力させることで、2の補数に変換してから第2のパルス列のパルス数をカウントする。

(もっと読む)

分周器

【課題】分周器としての性能を確保しつつ、消費電流を削減できる分周器の提供。

【解決手段】この発明は、分周回路10、30、50を直列接続したものであり、分周器の全体の消費電流を削減するために、分周回路10、30、50を、低電位側の第1グループG1と高電位側の第2グループG2とに分割させている。第1グループG1に属する分周回路10の低電位側の電源端子17は、低電位の電源VSSに接続されている。また、第2グループG2に属する分周回路30、50の高電位側の電源端子36、56は、高電位の電源VDDに接続されている。さらに、分周回路10の高電位側の電源端子16は、分周回路30、50の低電位側の電源端子37、57に接続されている。

(もっと読む)

周波数の即時調整が可能な節電型トリガー制御装置、および、その方法

【課題】周波数の即時調整が可能な節電型トリガー制御装置及びその方法を提供する。

【解決手段】本発明に係る装置は、少なくとも2つの信号入力端を有する信号制御ユニットと、計数制御ユニットと、クロック生成器と、からなる。2つの信号入力端はそれぞれ、トリガー回数を受信し、その後対応する回数の周波数逓増トリガー信号又は周波数逓減トリガー信号を生成する。計数制御ユニットにより受信した周波数逓増トリガー信号及び周波数逓減トリガー信号を計数する。クロック生成器により計数した周波数逓増トリガー信号又は周波数逓減トリガー信号の回数に基づき、出力周波数を線形逓増又は逓減する。本発明の装置は更に、電源コントローラーを有し、出力電圧を調整する。本発明は、システムのいかなる状態下でも、外部の制御により即時にシステムの周波数/電圧を線形調整でき、節電目的が達成される。

(もっと読む)

1 - 10 / 67

[ Back to top ]