国際特許分類[H03K27/00]の内容

国際特許分類[H03K27/00]に分類される特許

1 - 2 / 2

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

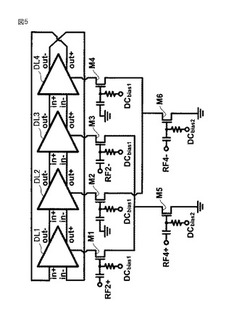

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

高速デバイド−バイ−ツー回路

高周波数デバイダ(124)は、複数の差動ラッチ(142,143)を含む。各ラッチは、クロス連結されたPチャネルトランジスタのペア(158,159および161,162)と可変抵抗素子(163,164)を含む。ラッチは、可変抵抗素子へ供給されるマルチ・ビット・デジタル制御値(CONTROL)を設定することによって高オペレーティング周波数でより低い出力抵抗を持つように制御される。高周波数で低下された出力抵抗を持つようにラッチを制御することは、ラッチの3dB帯域幅が、広いオペレーティング周波数レンジに維持されることを可能にする。かなりの直流バイアス電流が可変抵抗素子を渡って流れないように、可変抵抗素子は、ラッチの2つの差動出力ノード(146,147または152,153)の間に配置される。結果として、よい出力信号電圧振幅が高周波数で維持され、従来の差動ラッチデバイダにおける出力信号振幅の低下および電流消費増加と比較して、デバイダ電流消費は、高周波数であまり増加しない。 (もっと読む)

1 - 2 / 2

[ Back to top ]