国際特許分類[H03K3/282]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | 電気的パルスの発生回路;単安定回路,双安定回路,多安定回路 (1,702) | パルスの発生に用いられる回路形式または手段によって特徴づけられた発生器 (1,478) | 能動素子として内部または外部正帰還をもつバイポーラトランジスタを用いるもの (51) | 変成器以外の手段を帰還に用いるもの (50) | 一方のトランジスタの入力が他方のトランジスタの出力から得られる少なくとも2個のトランジスタを用いるもの,例.マルチバイブレータ (50) | 非安定 (29)

国際特許分類[H03K3/282]の下位に属する分類

出力の安定化 (1)

国際特許分類[H03K3/282]に分類される特許

1 - 10 / 28

電圧電流変換回路および電圧制御発振回路

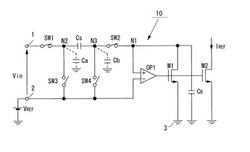

【課題】入力電圧に正確に対応した値の出力電流を得ることができる電圧電流変換回路およびその電圧電流変換回路で生成した電流を用いて高精度な発振周波数を得ることができるようにした電圧制御発振回路を提供する。

【解決手段】3容量Csと、容量CBと、スイッチSW1〜SW4と、オペアンプOP1と、トランジスタM1,M2とを備え、スイッチSW1,SW2がオン/オフするときスイッチSW3,SW4がオフ/オンするようにスイッチSW1〜SW4を制御し、電圧入力端子1に入力した入力電圧Vinに比例した電流IREFをトランジスタM1のドレインから出力する。

(もっと読む)

無線送信機

【課題】局部発振器の位相雑音性能の改善により、送信信号に含まれる隣接チャネル漏洩信号を大幅に低減することができる無線送信機を提供する。

【解決手段】ディジタルデータ信号を出力するデータ信号生成回路と、ディジタルデータ信号をディジタル/アナログ変換し、中間周波数のIF信号を出力するディジタル/アナログ変換回路と、IF信号と局部発振器から出力されるローカル信号とをミキシングし、無線周波数のRF送信信号を出力する直交ミキサ回路とを備えた無線送信機において、データ信号生成回路は、ディジタル/アナログ変換回路から出力されるIF信号の周波数が送信チャネルに応じて切り替わるディジタルデータ信号を出力する構成であり、局部発振器は、RF送信信号のチャネル周波数間隔のn倍(nは3以上の整数)の周波数間隔のローカル信号を切り替えて出力する構成である。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

発振回路

【課題】 クロック発振回路のジッタが音質に重要だとは気が付かなかったか、CMOSの発振回路のジッタ性能で十分だと思われていた。しかし、ジッタが多いと、音質的に十分でないことが判明した。そこで、高音質化のため低ジッタ化し、なおかつ高周波化、低電圧化、波形のエッジの急峻さ、波形の対称性を達成する必要性がある。

【解決手段】 CMOSよりもノイズ特性に優れるバイポーラトランジスタを使い、これをコンプリメンタリ接続にすることで、低ジッタ、高周波化、低電圧化、波形のエッジの急峻さ、高い対象性を得ることができた。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

発振回路

【課題】デューティの設計値に対して、発振信号の振幅や周波数の変化に依存したズレが生じない、デューティ調整部を有する発振回路を提供することを目的とする。

【解決手段】発振回路は、発振部からの第1の発振信号が入力され、この第1の発振信号の振幅及び周波数に依存しない立ち上がり及び立下り時間を持つ第2の発振信号を生成する第1の差動回路と、第2の発振信号が入力され、バイアス電圧源から与えられる電圧に依存したデューティを持つ第3の発振信号を生成する第2の差動回路とを有する。

(もっと読む)

基準信号発生装置

【課題】温度に関連する各種の周波数変動要素の影響を抑制して、高精度な基準周波数信号を発生する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、自走用制御電圧信号を推定して記憶する。制御部10は、温度センサ16からの温度検出信号に基づいて電圧制御発振器14の温度を観測して記憶する。制御部10は、ホールドオーバを検出すると、その時点での温度を検出するとともに(S101)、記憶した過去の温度を含み温度の時間変化率を算出する(S102)。制御部10は、予め設定した制御補正値算出用係数を読み出し(S103)、当該係数により設定される演算式に、検出した温度および算出した温度の時間変化率を代入して、制御補正値を算出する(S104)。制御部10は、この制御補正値に基づいて自走用制御電圧信号を補正し、電圧制御発振器14へ与える。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

1 - 10 / 28

[ Back to top ]