国際特許分類[H03K5/01]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | パルスの整形 (700)

国際特許分類[H03K5/01]の下位に属する分類

増幅によるもの (32)

持続時間の増大によるもの;持続時間の減少によるもの (189)

振幅制限によるもの,しきい値によるもの,スライスによるもの,すなわち振幅制限としきい値の結合によるもの (389)

立上りまたは立下りの峻度の増大によるもの (76)

国際特許分類[H03K5/01]に分類される特許

1 - 10 / 14

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

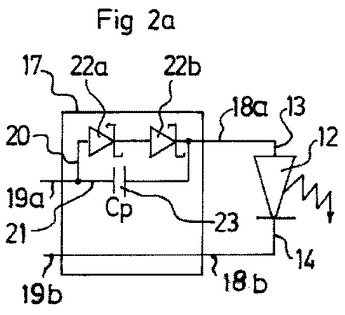

光電素子の超高速駆動用受動素子回路

本発明は、光電素子の超高速駆動回路において、時間400ps以下のエッジを有する電圧矩形波の発生器、ならびに、光電素子の電源端子(13)に直列に接続するように適合された出力、および、電圧矩形波発生器に接続され、そこで形成される電圧矩形波を受け取る入力を備える制御パルス成形回路(17)を含み、前記入力端子と前記出力端子の間に、ゼロでない閾値電圧を有する受動整流回路(22a、22b)からなる第1の分岐(20)であって、その受動整流回路(22a、22b)が第1の分岐内において直列をなし、光電素子の前記電源端子(13)に対して順方向をなす第1の分岐(20)と、第2の容量性分岐(21)とが互いに並列につながれていることを特徴とする駆動回路に関する。  (もっと読む)

(もっと読む)

パルス伝送線路、パルス供給装置及びプラズマ処理装置

【課題】電気パルスを高効率かつ安全に伝送するパルス伝送線路を提供する。

【解決手段】第1の同軸ケーブル116の内部導体118の電源側端は、入力ポート104の第1の入力端子106に接続され、外部導体120の電源側端は開放される。内部導体118の負荷側端は、コモンモードリアクトル136の第1の巻線138を経由して出力ポート110の第1の出力端子112に接続され、外部導体120の負荷側端は、第1の抵抗器132を経由してグランドに接続される。第2の同軸ケーブル122の内部導体124の電源側端は、入力ポート104の第2の入力端子108に接続され、外部導体126の電源側端は開放される。内部導体124の負荷側端は、コモンモードリアクトル136の第2の巻線140を経由して出力ポート110の第2の出力端子114に接続され、外部導体126の負荷側端は、第2の抵抗器134を経由してグランドに接続される。

(もっと読む)

信号処理装置

【課題】パルスの立上がりと立下り遅延時間を独立して調整することのできる遅延回路を備えた信号処理装置を得る。

【解決手段】シリアル接続された複数の信号処理回路と、第1の抵抗と、上記第1の抵抗に直列接続されたダイオードと、上記第1の抵抗とダイオードの直列回路に並列接続された第2の抵抗と、上記第1の抵抗およびダイオードと第2の抵抗の並列回路に接続され、グランドに接地されたキャパシタと、上記並列回路およびキャパシタの後段に接続された増幅器とを有して構成され、上記それぞれの信号処理回路の後段に接続された遅延回路を備える。

(もっと読む)

半導体回路および試験装置

【課題】電源電圧のリップルが信号処理回路に及ぼす影響を低減する。

【解決手段】第1信号処理回路10は、第1信号S1に所定の信号処理を施し、その特性値に変化を与えて第2信号S2を出力する。第2信号処理回路12は、第2信号S2に所定の信号処理を施し、その特性値に変化を与えて第3信号S3を出力する。第1、第2スイッチング電源20、22はそれぞれ、第1、第2信号処理回路10、12に対し電源電圧Vdd1、Vdd2を供給する。第1信号処理回路10が第1信号S1の特性値に与える変化量と、第2信号処理回路12が第2信号S2の特性値に与える変化量はそれぞれ、電源電圧Vdd1、Vdd2に対する依存性を有する。第1、第2スイッチング電源20、22の位相はそれぞれ、第1信号S1の特性値の変化量とその目標値との誤差と、第2信号S2の特性値の変化量とその目標値との誤差がキャンセルするように設定される。

(もっと読む)

歪曲されたデューティ比を補正するDLLクロック生成回路

【課題】本発明は、デューティの歪曲を補正したDLLクロックを生成するDLLクロック生成回路を提供する。

【解決手段】本発明のDLLクロック生成回路は、 第1のクロック及び第2のクロックの入力により、第1の内部クロック及び第2の内部クロックを生成し、第1の内部クロックのデューティ比により生成された基準信号に基づき、第1の内部クロック及び第2の内部クロックのデューティを補正するデューティ補正バッファと、デューティ補正バッファに連結しており、第1の内部クロックのイネーブル動作により第1のレベルに遷移され、第2の内部クロックのイネーブル動作により第2のレベルに遷移される、DLLクロックを生成するエッジトリガー部を含む。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

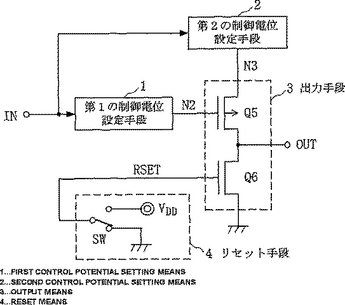

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

1 - 10 / 14

[ Back to top ]