国際特許分類[H03K5/13]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 単一の出力をもち,かつ入力信号を変換して所望の時間間隔を有するパルスを与える配置 (668)

国際特許分類[H03K5/13]の下位に属する分類

時間参照信号,例.クロック信号の使用によるもの (174)

遅廷線の使用によるもの (118)

共振回路の使用によるもの

国際特許分類[H03K5/13]に分類される特許

1 - 10 / 376

データドライバ、表示パネル駆動装置及び表示装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

遅延回路及びそれを用いた半導体装置

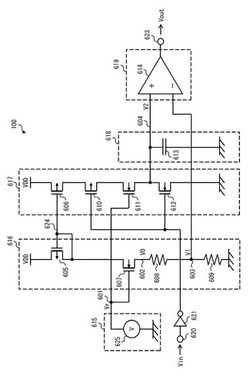

【課題】入力信号に精度の高い遅延を付加した出力信号を生成することが可能な遅延回路を提供すること。

【解決手段】本発明にかかる遅延回路は、第1電流I0及び第1電流I0と略同一の第2電流I0を生成する電流ミラー回路と、ゲートに基準電圧Vrが印加されソース−ドレイン間に第1電流I0が流れることにより電圧V0を生成するトランジスタ607と、電圧V0に応じた参照電圧V1を生成する抵抗素子608,609と、コンデンサ613と、第2電流I0の電荷をコンデンサ613に蓄積し、又は、コンデンサ613に蓄積された電荷を放出する充放電部と、充放電部とコンデンサ613との間に設けられ、ゲートに基準電圧Vrが印加されソース−ドレイン間に第2電流I0が流れることにより、比較電圧V2を生成するトランジスタ611と、比較電圧V2と参照電圧V1とを比較し比較結果を出力信号Voutとして出力する電圧比較部619と、を備える。

(もっと読む)

半導体記憶装置

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システム

【課題】簡易な構成で時間制御を制御することができる可変遅延デバイス、デバイス調整方法、及びポジトロン放出断層撮影システムを提供する。

【解決手段】可変遅延デバイス240は、飛行時間ガンマ線検出システムの光センサ140に接続され、複数の導電性ピン210、215が搭載された基板205を含む。複数の導電性ピンのうちの第1に接続している第1の端子、及び複数の導電性ピンのうちの第2に接続している第2の端子もまた、基板205に搭載されている。ジャンパ220は、基板205に対して所定の距離で複数の導電性ピンを電気的に接続し、可変遅延デバイス240の時間遅延は、複数の導電性ピン210、215とジャンパ220とによって形成される第1及び第2の端子間の電気経路に基づいて決定される。

(もっと読む)

半導体装置

【課題】調整コードの変化に伴うジッタの発生が低減されたDLL回路を提供する。

【解決手段】内部クロック信号ECLKを受けるインバータ回路210〜217と、内部クロック信号OCLKを受けるインバータ回路220〜227とを有し、調整コードC0〜C7を受けて選択されたインバータ回路の出力を合成することによって、内部クロック信号LCLKの位相を16段階に調整する。インバータ回路210,220は内部クロック信号LCLKの位相を1段階変化させる能力を有し、インバータ回路211〜217,221〜227は内部クロック信号LCLKの位相を2段階変化させる能力を有する。このように、内部クロック信号LCLKの位相を調整するインバータ回路の最大能力が抑制されていることから、調整コードの変化に伴うジッタの発生が低減される。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

遅延回路

【課題】電源電圧が変わっても一定の遅延時間を有する遅延回路を提供する。

【解決手段】遅延回路10では、第1、第2チャネルの第1、第2絶縁ゲート電界効果トランジスタP11〜P1n、N11〜N1nのゲート電極同士および第1電極同士が接続された相補型電界効果トランジスタは、ゲート電極に入力される入力信号Vinを反転した出力信号Voutを出力する。第1チャネルの第3絶縁ゲート電界効果トランジスタP21〜P2nは第1電源電圧Vccが印加される第1電源端子16と第1絶縁ゲート電界効果トランジスタP11〜P1nの第2電極との間に接続され、第1電源電圧Vccをゲート電極に入力される第1制御信号Vcに応じて定まる出力電圧Vccoutに変換して出力する。第1制御信号生成回路13は、第1電源電圧Vccに応じて第1制御信号Vcを生成し第3絶縁ゲート電界効果トランジスタP21〜P2nのゲート電極に出力する。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

1 - 10 / 376

[ Back to top ]