国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

71 - 80 / 305

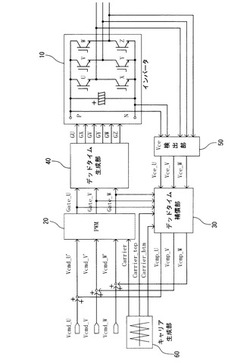

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

リファレンスリークの発生や位相ノイズを低減できるPLL回路

【課題】リファレンスリークを低減することができ、位相ノイズを抑制することができるPLL回路を提供する。

【解決手段】切り替え機能付き周波数位相比較器は、入力されるロック検出信号に基づいて、入力される2つの信号の立ち上がりエッジを検出することにより当該2つの信号の位相差を検出する周波数比較と、入力される2つの信号の電圧レベルを検出することにより当該2つの信号の位相差を検出する位相比較とを切り替えて行う。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

71 - 80 / 305

[ Back to top ]