国際特許分類[H03K5/26]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 入力信号特性,例.傾斜,積分,にもとづいてパルスまたはパルス列をお互いに比較するための2つ以上の入力と1つの出力をもつ回路 (310) | 入力信号特性が持続時間,間隔,位置,周波数または順序であるもの (305)

国際特許分類[H03K5/26]に分類される特許

81 - 90 / 305

局部発振器

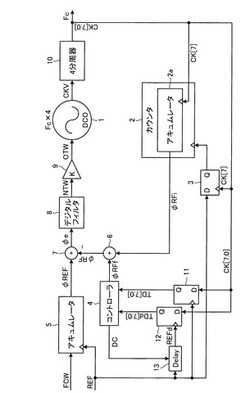

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

パワーオンリセット信号を制御するためのシステムおよび方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

位相検出回路およびPLL回路

【課題】2つのクロック信号の位相比較に基づき生成する2つのパルス信号の遅延時間を極力短くすることができ、かつ確実にリセットできる位相検出回路および該位相検出回路を備えたPLL回路を提供すること。

【解決手段】位相検出回路は、位相比較を行う2つのクロック信号の論理和信号と論理積信号とに基づき、進相側と遅相側の2つのパルス信号の生成に用いる一方の出力を、前記位相比較を行う準備動作状態と、前記位相比較を行った回路動作状態とに切り替えて保持するラッチ回路を備えている。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

81 - 90 / 305

[ Back to top ]